Trench type MOSFET device and preparation method thereof

A trench type, device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of difficulty in connecting the bottom p+ region, increase in the size of the original cell, etc., and achieve simple device structure and preparation process, The effect of fine shielding, which is conducive to the promotion of applications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0042] The method of the present invention is applicable to various SiC and other semiconductor field effect transistors, such as MOSFETs, IGBTs, etc., and SiC MOSFETs are taken as an example below for illustration.

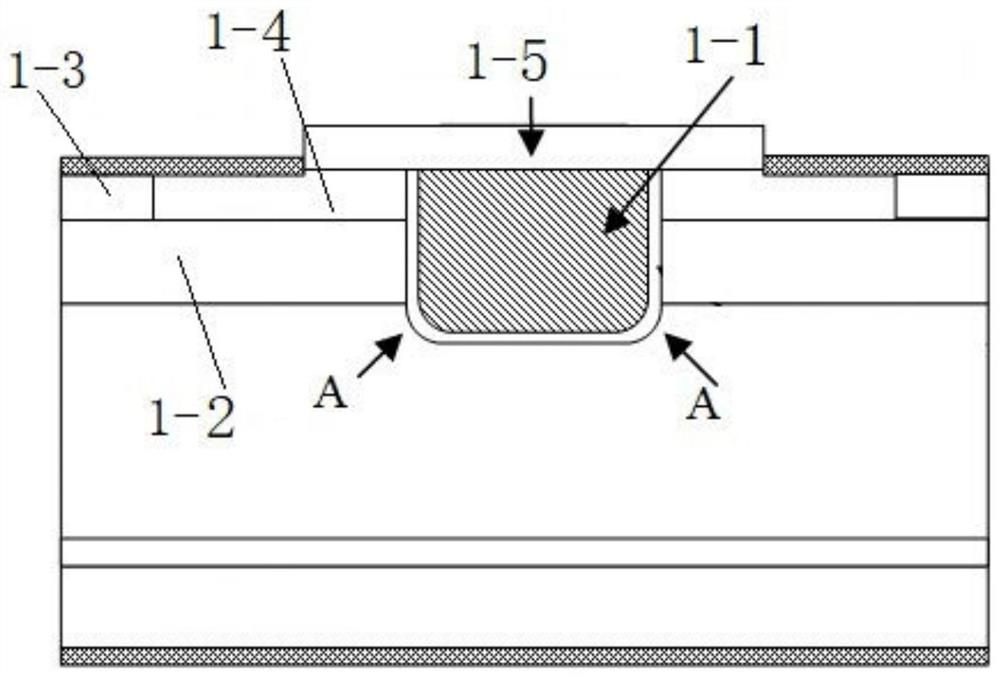

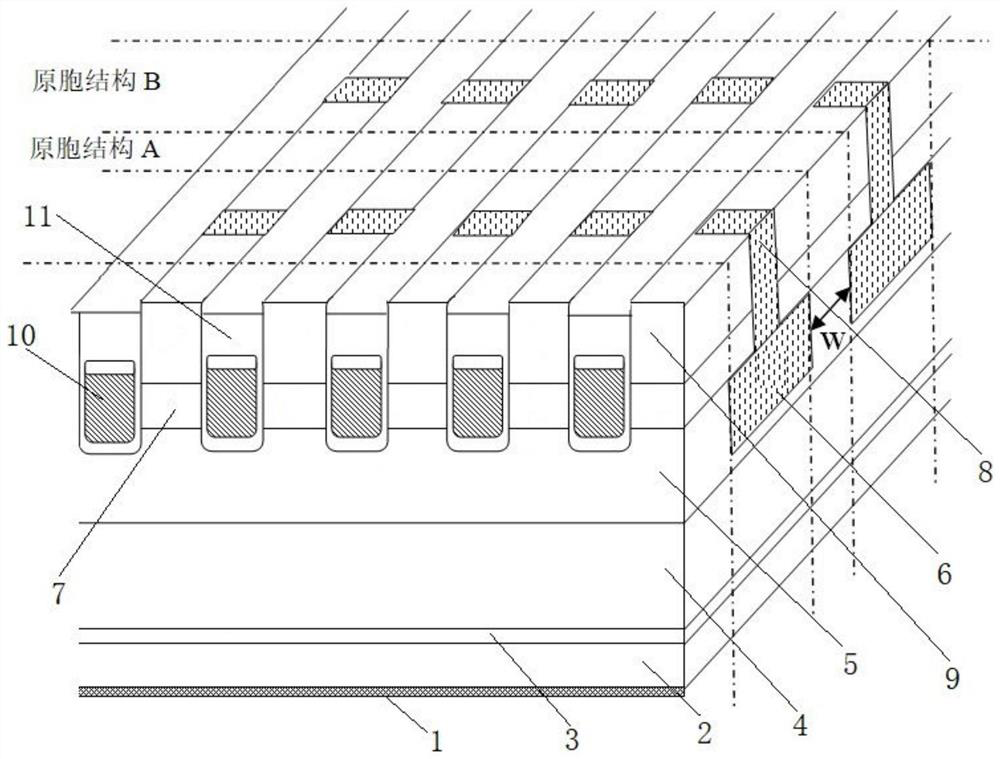

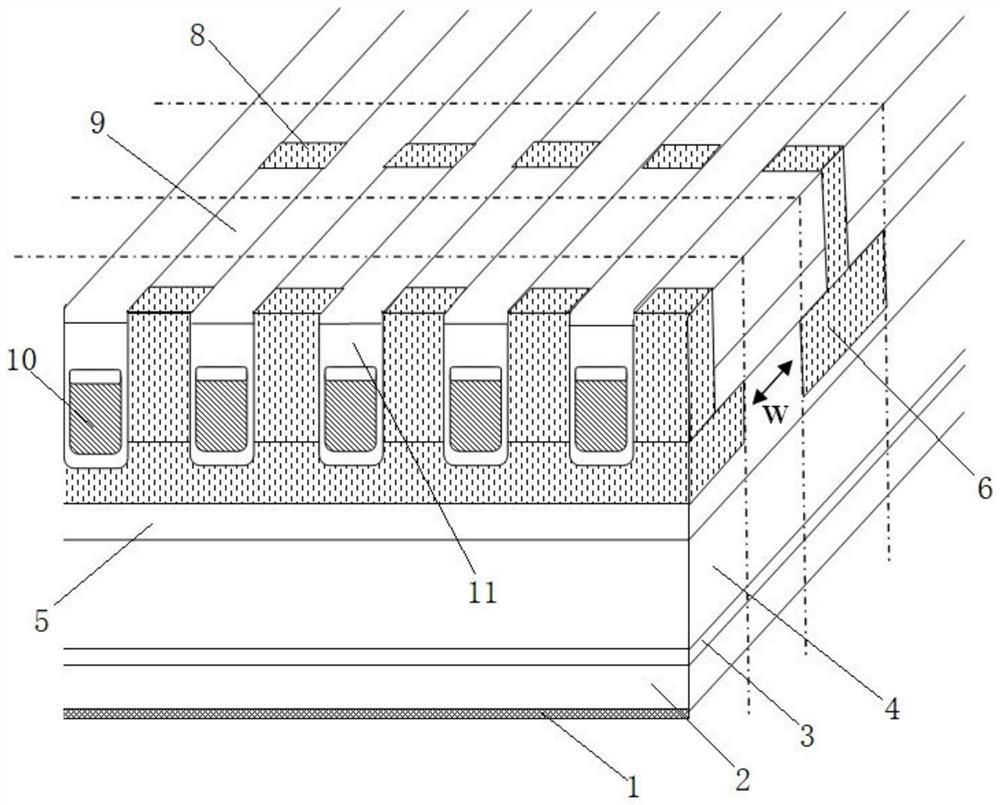

[0043] combine figure 2 with image 3 As shown, this embodiment provides a trench type MOSFET device, which includes drain 1, n+ substrate 2, n+ buffer layer 3, n-drift layer 4, CSL layer 5, p+ buried layer 6, P well 7, p+ region 8 and n+ region 9, gate dielectric, polysilicon gate 10, gate-source isolation dielectric 11, source electrode; the active region of the device is composed of two types of primitive cells with different structures, one type of primitive cells is MOSFET conductive cell A (primary cell cross-section such as figure 2 shown); another type of primitive cell is the primitive cell B that shields the electric field of the trench gate structure (the cross section of the primitive cell is as follows image 3 As shown), the p+ buried layer in ...

Embodiment 2

[0053] The n-type doping and p-type doping mentioned in the embodiment of the present invention are relative terms, and can also be referred to as the first doping and the second doping, that is, the interchange of n-type and p-type is also applicable to devices . Meanwhile, the device structure in the embodiment of the present invention is not only applicable to SiC, but also applicable to other semiconductor materials such as Si, GaN, Ga2O3, etc. In the embodiment of the present invention, SiC is taken as an example.

[0054] Embodiment 2 provides a method for preparing a trench MOSFET device, specifically as follows:

[0055] Such as Figure 4 As shown, an n+ buffer layer 3, an n-drift layer 4, and an n-type CSL layer 5 (current spreading layer) are epitaxially extended on a conductive type n+ substrate 2 in sequence. The concentration and thickness of the n-drift layer 4 are determined by the withstand voltage design of the device, and the general concentration is great...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More