FPGA-based Ethernet port flow rate limiting system and method

A technology of Ethernet and flow limitation, which is applied in the field of FPGA-based Ethernet port flow rate limiting system, which can solve the problems that it is difficult to meet the requirements of controllable substation switches, and the Ethernet switch chip does not support the port rate limit function, etc., to meet the requirements Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described below in conjunction with the description of the drawings and specific embodiments.

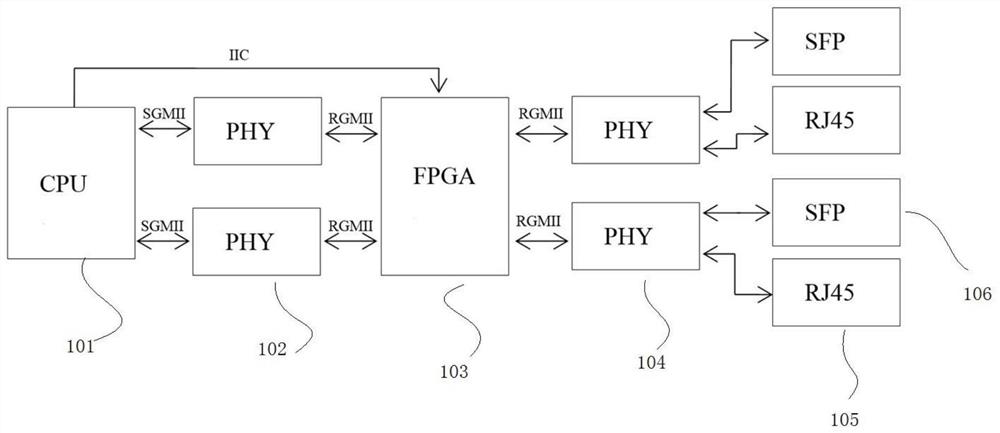

[0021] Such as Figure 1 to Figure 3 As shown, an FPGA-based Ethernet port flow rate limiting system includes a CPU (Central Processing Unit) unit 101, a first PHY (port physical layer) unit 102, an FPGA (Field Programmable Logic Gate Array) unit 103, a first Two PHY units 104 and a network interface 105, the network interface 105 is bidirectionally connected to the input and output of the second PHY unit 104, the second PHY unit 104 is bidirectionally connected to the input and output of the FPGA unit 103, and the FPGA unit 103 Two-way connection with the input and output of the first PHY unit 102, the two-way connection between the first PHY unit 102 and the SGMII interface input and output of the CPU unit 101, the output of the CPU unit 101 is connected to the FPGA unit through the IIC bus Connect with 103.

[0022] The CPU unit 101 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com