DRAM fault correlation analysis method based on sequence mode

A technology of association analysis and sequence mode, applied in the computer field, can solve problems such as increasing the complexity of CPU design, and achieve the effects of optimizing analysis execution efficiency, optimizing CPU design, and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

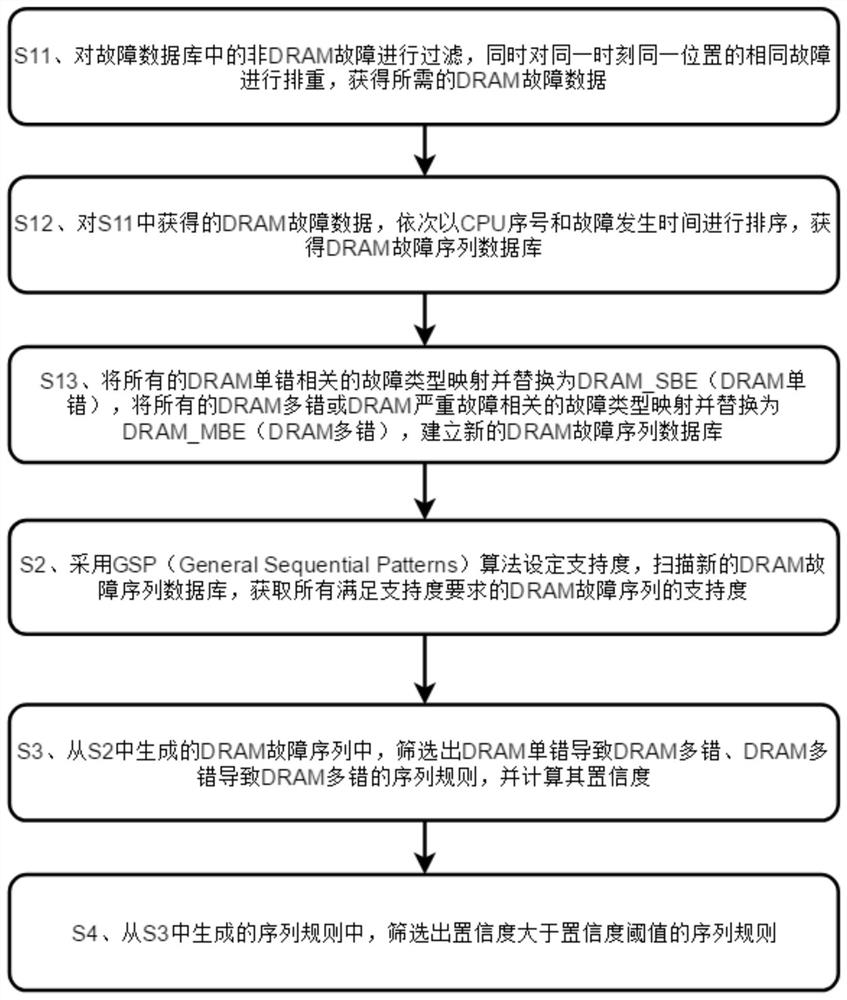

[0019] Embodiment: a kind of DRAM failure association analysis method based on sequence pattern, comprises the following steps:

[0020] S11. Filter the non-DRAM faults in the fault database, and at the same time deduplicate the same faults at the same location at the same time, to obtain the required DRAM fault data;

[0021] S12. Sorting the DRAM fault data obtained in S11 sequentially by CPU serial number and fault occurrence time to obtain a DRAM fault sequence database;

[0022] S13. Map and replace all fault types related to DRAM single faults with DRAM_SBE (DRAM single faults), map and replace all fault types related to DRAM multiple faults or serious DRAM faults with DRAM_MBE (DRAM multiple faults), and This reduces the DRAM fault sequence database obtained in S12 to a fault sequence data set with only two fault types (DRAM_SBE and DRAM_MBE), and establishes a new DRAM fault sequence database;

[0023] S2. Use the GSP (General Sequential Patterns) algorithm to set the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com