A coarse-grained dynamic reconfigurable processor and its data processing method

A data processing and processor technology, applied in the direction of electrical digital data processing, architecture with a single central processing unit, instruments, etc., can solve the problems that cannot meet the general hardware programming flexibility, high computing performance and high energy efficiency at the same time, Achieve the effect of avoiding memory access conflicts, reducing waiting time, and reducing configuration time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

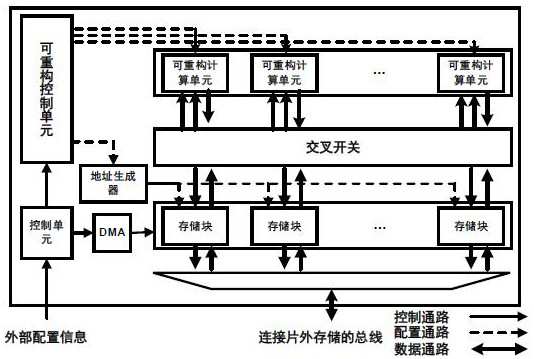

[0060] This embodiment discloses a common coarse-grained dynamic reconfigurable processor in the field, and its architecture schematic diagram is as follows figure 1 As shown, the processor includes the following main units: a control unit; a reconfigurable control unit; a reconfigurable computing array; an on-chip storage pool composed of a plurality of on-chip storage blocks; a conflict-free address for generating the access addresses of the on-chip storage blocks A generator; a direct memory access (DMA) module and a data distribution module between the DMA and a storage pool.

[0061] The relationship between the main units is as follows: the control unit sends the configuration information obtained through analysis to the reconfigurable control unit; the reconfigurable control unit generates all options in the reconfigurable computing array according to the configuration information The selection signal of the channel completes the reconfiguration of the computing array; ...

Embodiment 2

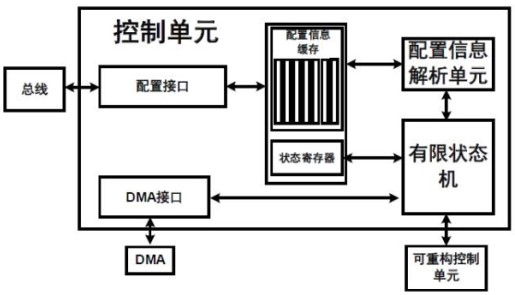

[0063] On the basis of Embodiment 1, the schematic diagram of the structure of the control unit is as follows figure 2 As shown, it mainly includes the following main units: configuration interface, configuration information cache, configuration information parsing unit, finite state machine, DMA control interface, status register, etc. The relationship between the main units is as follows: the reconfigurable processor disclosed in the present invention actively or passively receives external configuration information through the configuration interface; when in the configuration information prefetching mode, the configuration interface stores the received configuration information into In the configuration information cache; the configuration information parsing unit reads the configuration information from the configuration information cache, and then decomposes it into multiple sub-configuration words, and then parses it according to the bit field meaning of the agreed conf...

Embodiment 3

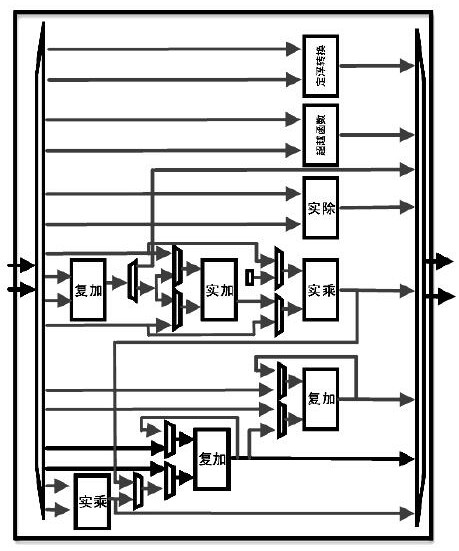

[0065] On the basis of Embodiment 1 or Embodiment 2, the schematic diagram of mapping operators to reconfigurable computing arrays is as follows: image 3 , Figure 4 , Figure 5 shown. Reconfigurable computing arrays are interconnected by reconfigurable computing units, where image 3 and Figure 4 Both are single reconfigurable computing units. The reconfigurable calculation unit includes several basic calculation components according to the requirements of the application field. In this embodiment, it includes complex multiplication, complex addition, real number multiplication, and real number division. In addition, it also includes a selection path between these calculation components, so it can be Different functions can be realized through different gating of the selection channel, such as image 3 As shown, the multiple addition function is realized by gating, such as Figure 4 As shown, the pipelined complex multiplication and accumulation function is realized b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More