Method for calculating maximum absolute output error of approximate arithmetic logic circuit

A technology of arithmetic logic and calculation method, which is applied in the calculation field of the maximum absolute output error of an approximate arithmetic logic circuit, and achieves the effect of high operation efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

[0034] The calculation method of the maximum absolute output error of a kind of approximate arithmetic logic circuit that the present invention proposes, it comprises the following steps:

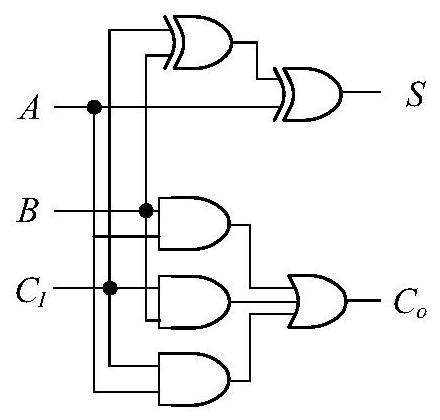

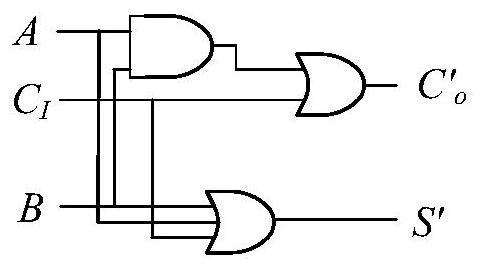

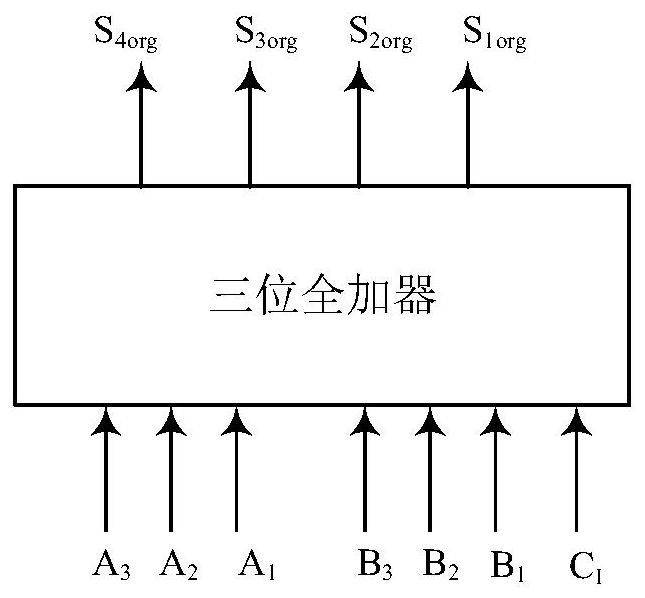

[0035] Step 1: Let Z ap Indicates an approximate arithmetic logic circuit, Z ap There are N input variables, Z ap There are K output variables; and let Z org means Z ap The corresponding primitive arithmetic logic circuit, Z org There are also N input variables, Z org There are also K output variables, Z org The output of is error-free; the Z ap The output is defined as O ap , the Z org The output is defined as O org , will O ap The i-th bit of is denoted as O iap , will O org The i-th bit of is denoted as O iorg , and stipulate O ap The highest and lowest bits correspond to O Kap and O 1ap , stipulate O org The highest and lowest bits cor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com