A PTP-based multi-link delay jitter optimization method and device

A technology of time delay jitter and optimization method, which is applied in synchronization devices, wireless communication, electrical components, etc., can solve problems such as terminal clock fluctuation, and achieve the effects of high accuracy, high reliability and good timeliness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

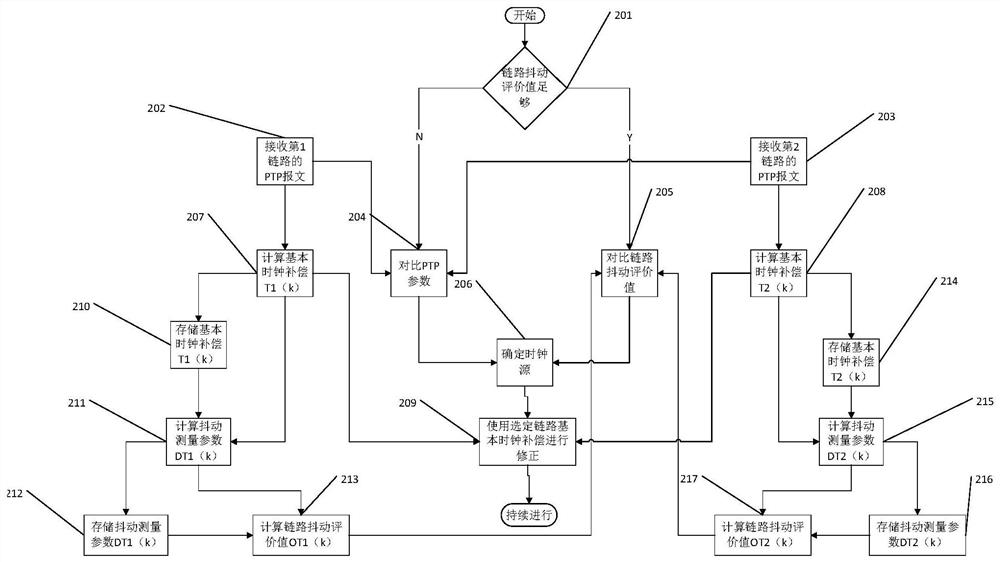

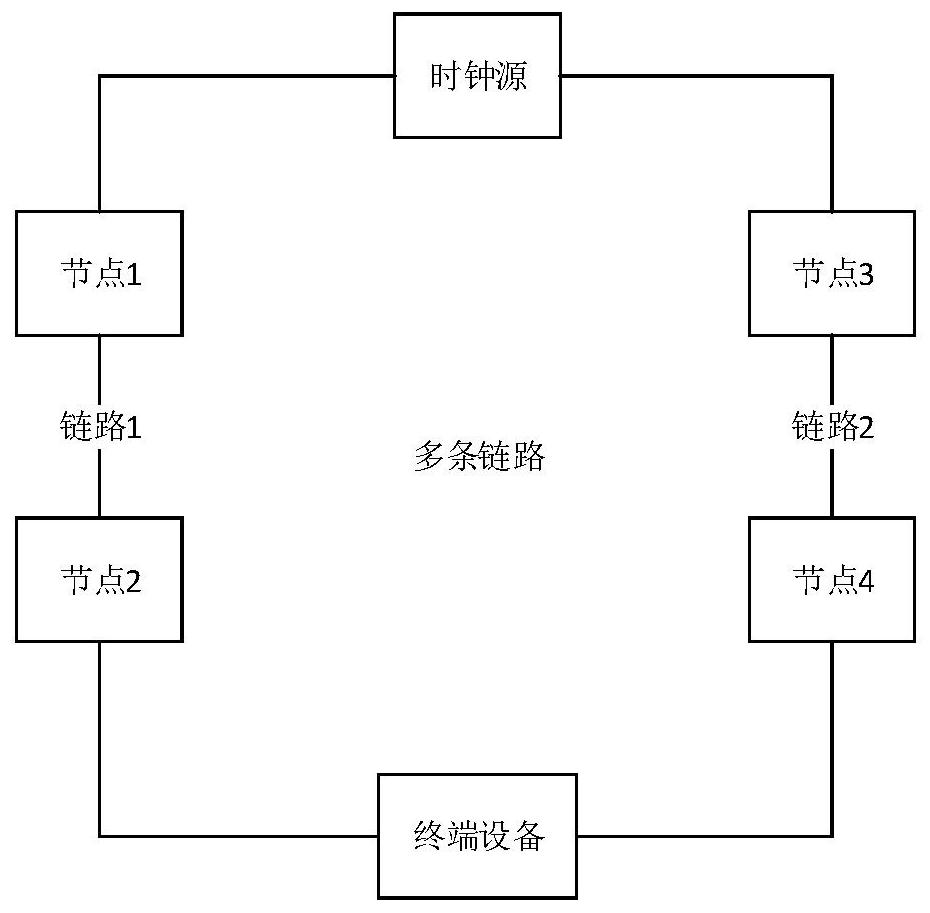

[0040] The PTP-based multi-link delay jitter optimization method of the present invention calculates the jitter parameters of different links by recording the basic clock compensation of different links, and calculates the link jitter evaluation value of different links by means of weighted average. After evaluating the jitter values of different links, select the basic clock compensation of a link as the clock compensation value for this adjustment. Compared with the prior art, the present invention has the advantages of high reliability, high accuracy, strong timeliness, etc., and avoids the disadvantages that the link fixation cannot be selected and the jitter is large when the PTP terminal performs multi-link clock synchronization. Better guarantee of clock synchronization.

[0041] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the presen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com