Efficient inter-chip interconnect topology for distributed parallel deep learning

An interconnection structure and inter-chip technology, applied in the field of computing, can solve problems such as inability to divide multiple computing tasks, long connection line delays, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

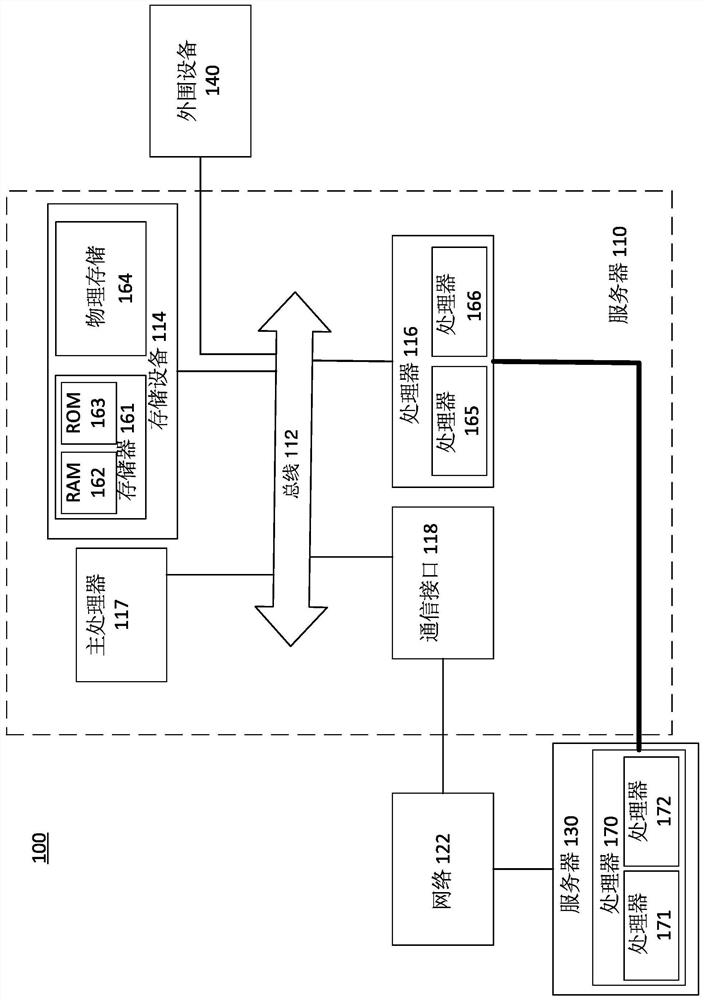

[0018] Reference will now be made in detail to the exemplary embodiments, examples of which are illustrated in the accompanying drawings. For the following description, please refer to the accompanying drawings. Unless otherwise specified, the same reference numerals in different drawings indicate the same or similar elements. The implementations set forth in the following description of the exemplary embodiments do not represent all implementations consistent with the invention. Rather, they are merely examples of apparatus and methods consistent with aspects of the invention described in the appended claims.

[0019] Distributed computing is the field of computer science that studies distributed systems. A distributed system is a system whose components are located on different networked computers that communicate and coordinate their actions by passing messages to each other.

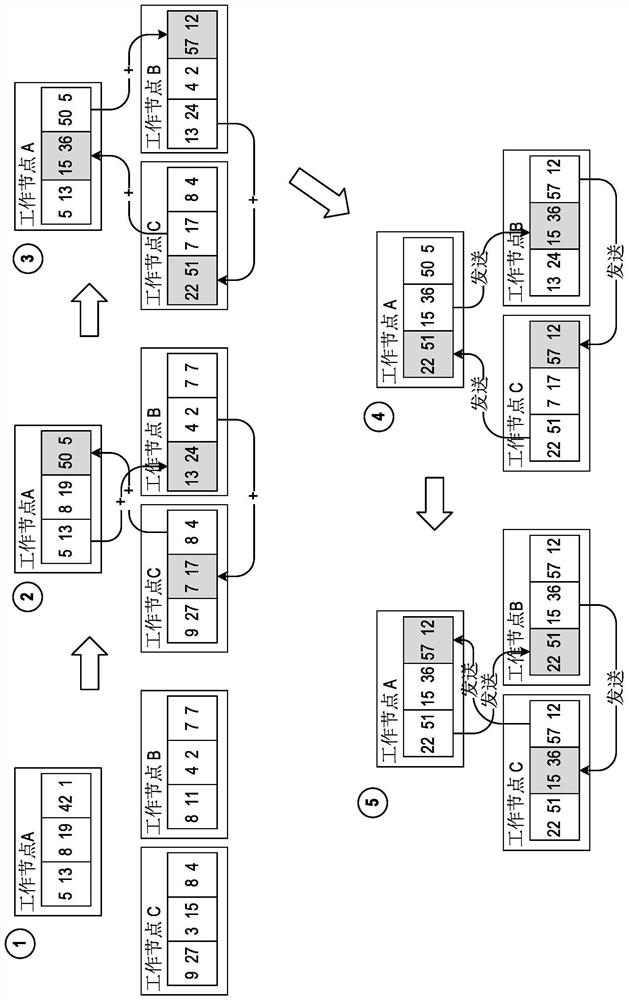

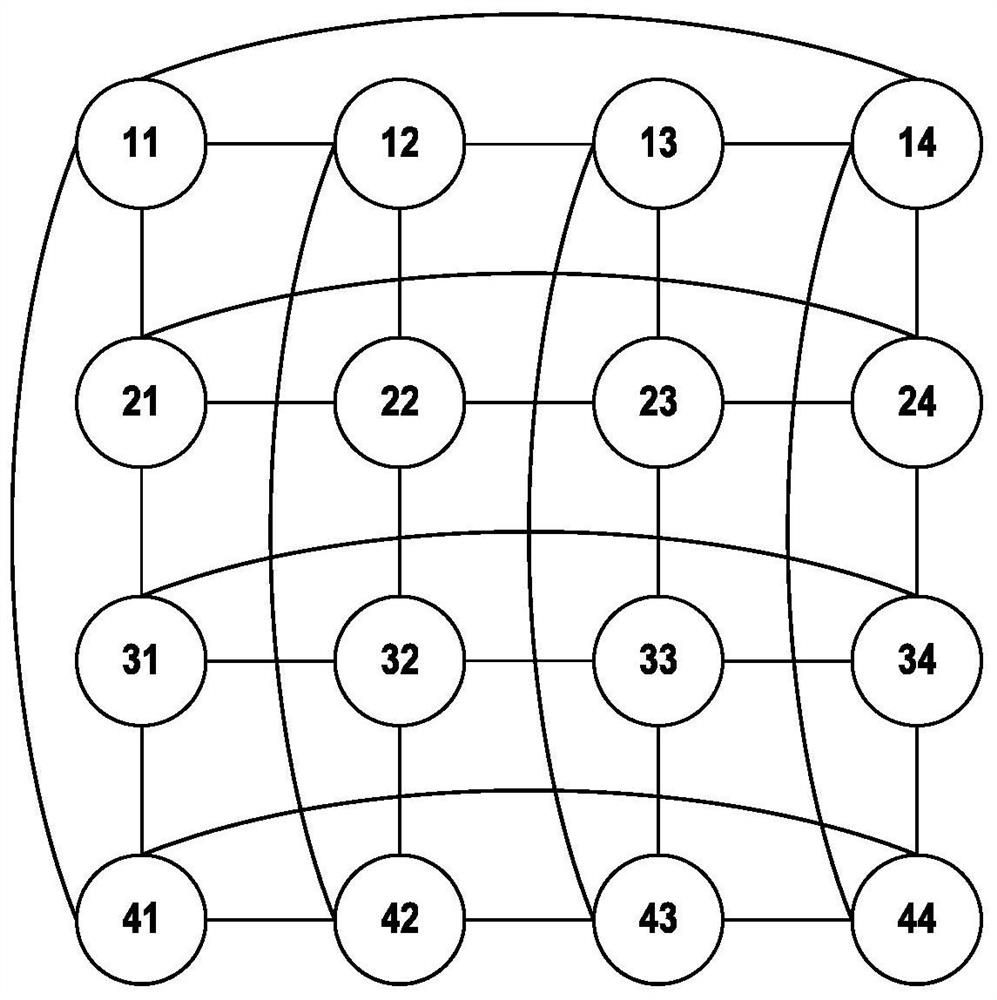

[0020] Distributed deep learning is an implementation of deep learning algorithms. Since deep ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com