Online debugging method for FPGA (Field Programmable Gate Array) with dynamically variable sampling frequency

A technology of sampling frequency and debugging method, which is applied in the field of FPGA, can solve the problems of little meaning of data, limited storage capacity of the total number of samples, low debugging efficiency, etc., and achieve the effect of improving efficiency and reducing invalid data with constant sampling repetition

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

[0029] The application discloses an FPGA online debugging method with a dynamically variable sampling frequency. The implementation process of the method is as follows:

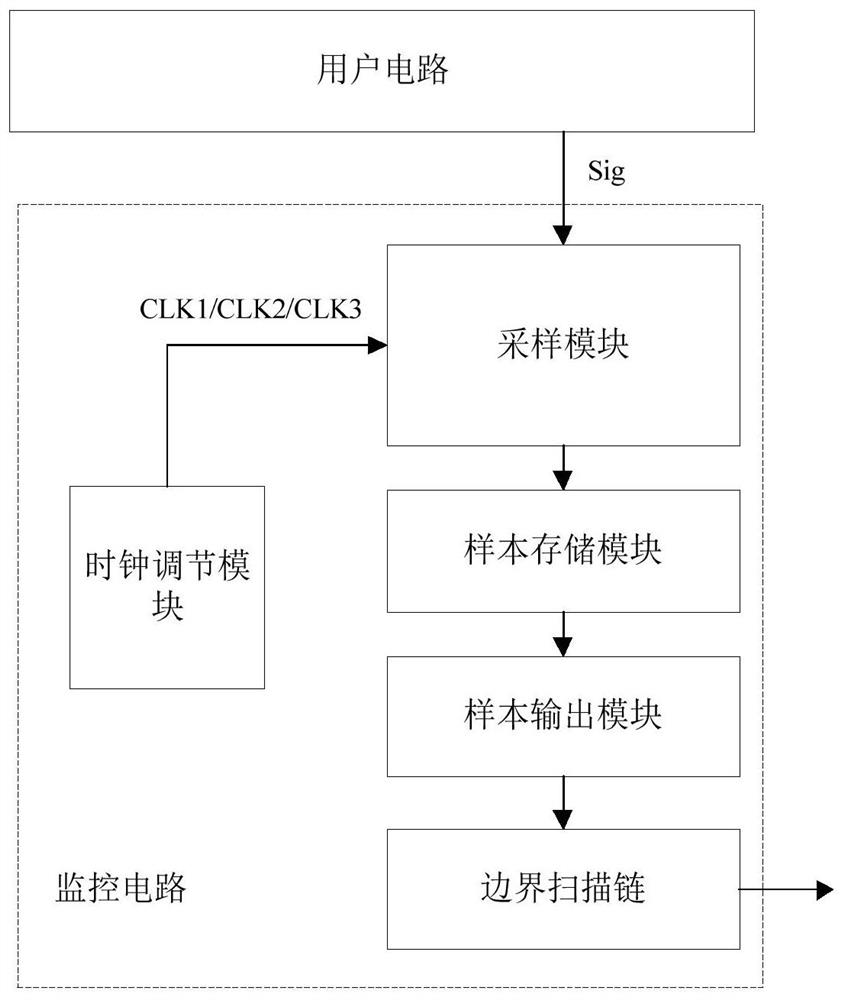

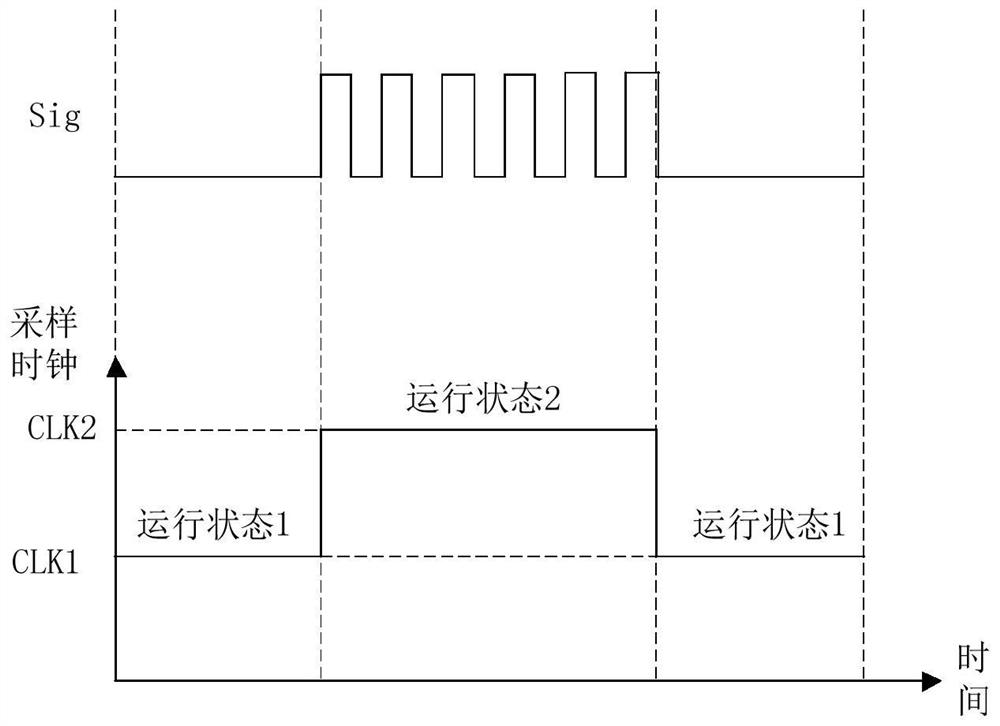

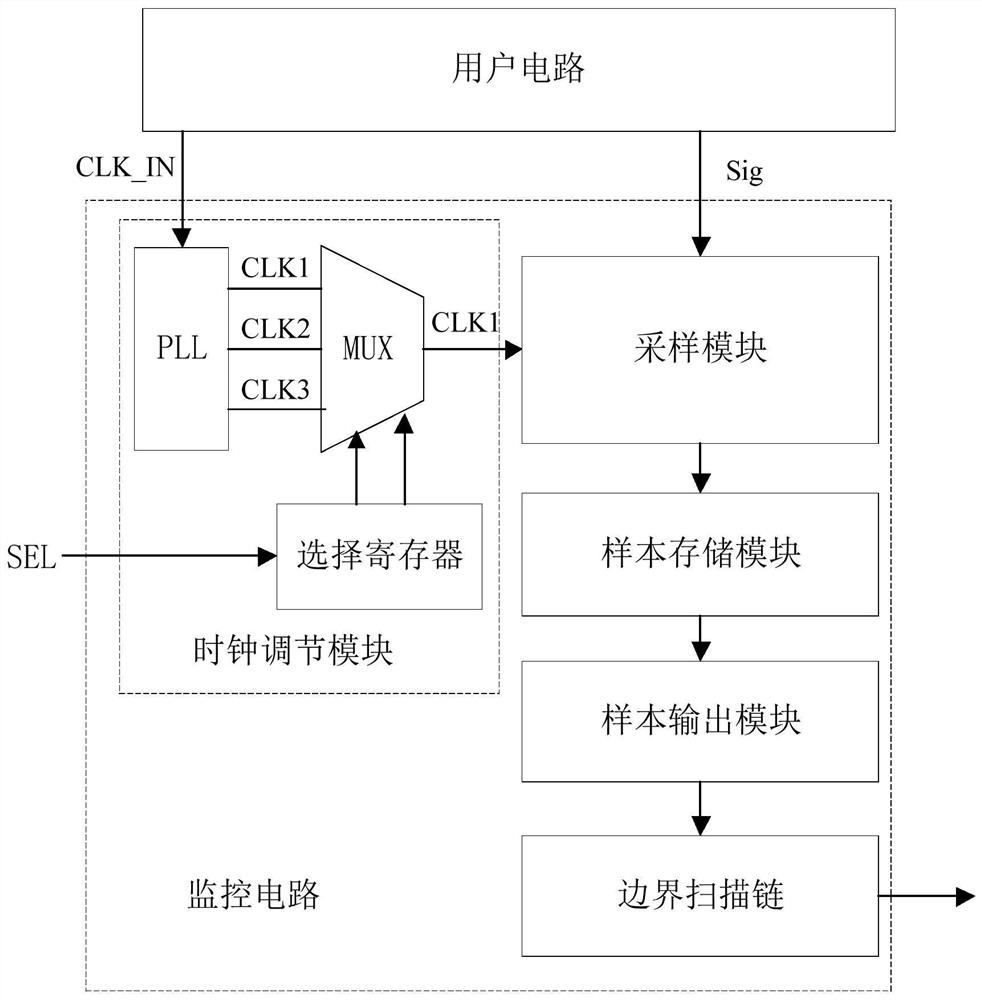

[0030] When debugging the user circuit, the configuration code stream corresponding to the global circuit composed of the user circuit and the monitoring circuit is loaded onto the FPGA. The global circuit in this application refers to the entire circuit structure that needs to be implemented using programmable logic resources on the FPGA and run on the FPGA. The global circuit includes at least the user circuit, and the user circuit is the circuit structure used to realize the user-designed function in the global circuit. When debugging the user circuit, the global circuit not only includes the user circuit, but also includes a monitoring circuit connected to the user circ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More