Multi-core processor circuit

A processor circuit, multi-core technology, applied in the direction of instruments, simulators, computer control, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

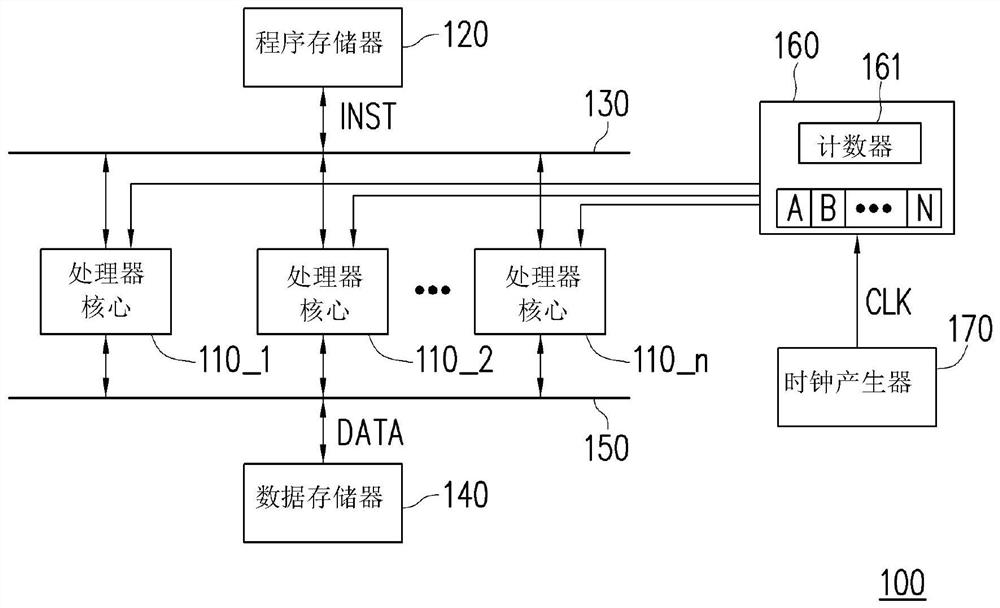

[0025] figure 1 It is a schematic diagram of a multi-core processor circuit according to an embodiment of the present invention. Please refer to figure 1 , in this embodiment, the multi-core processor circuit 100 includes a plurality of processor cores 110_1-110_n, a program memory 120, a first bus 130, a data memory 140, a second bus 150, a control circuit 160 and a clock generator 170, wherein the program memory 120 is used to store at least one program instruction INST, and the data memory 140 is used to store at least one program data DATA. Wherein, n is a positive integer greater than or equal to two.

[0026] The first bus bar 130 is coupled between the processor cores 110_1 - 110 — n and the program memory 120 , and the second bus bar 150 is coupled between the processor cores 110_1 - 110 — n and the data memory 140 . The control circuit 160 is coupled to the processor cores 110_1 - 110_n to enable these processor cores 110_1 - 110_n one by one, and disable the rest ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap