Intelligent super-junction MOS device and manufacturing method thereof

A MOS device and intelligent technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of low isolation voltage and no real isolation, and achieve high isolation voltage and smooth electric field distribution.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be described in further detail below in conjunction with the accompanying drawings.

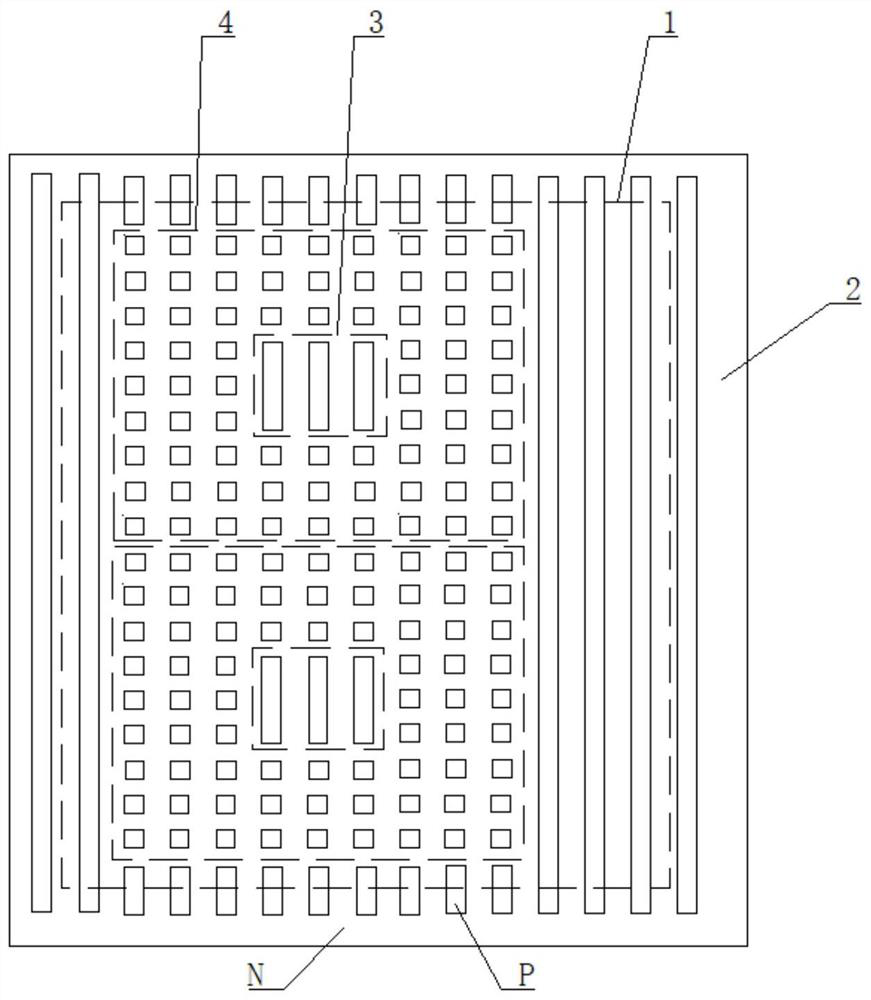

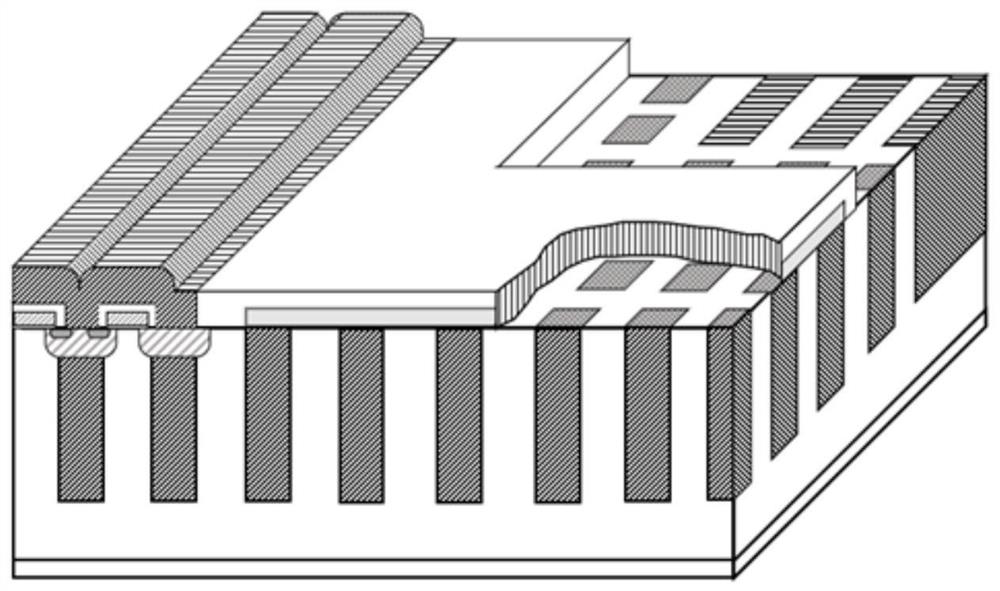

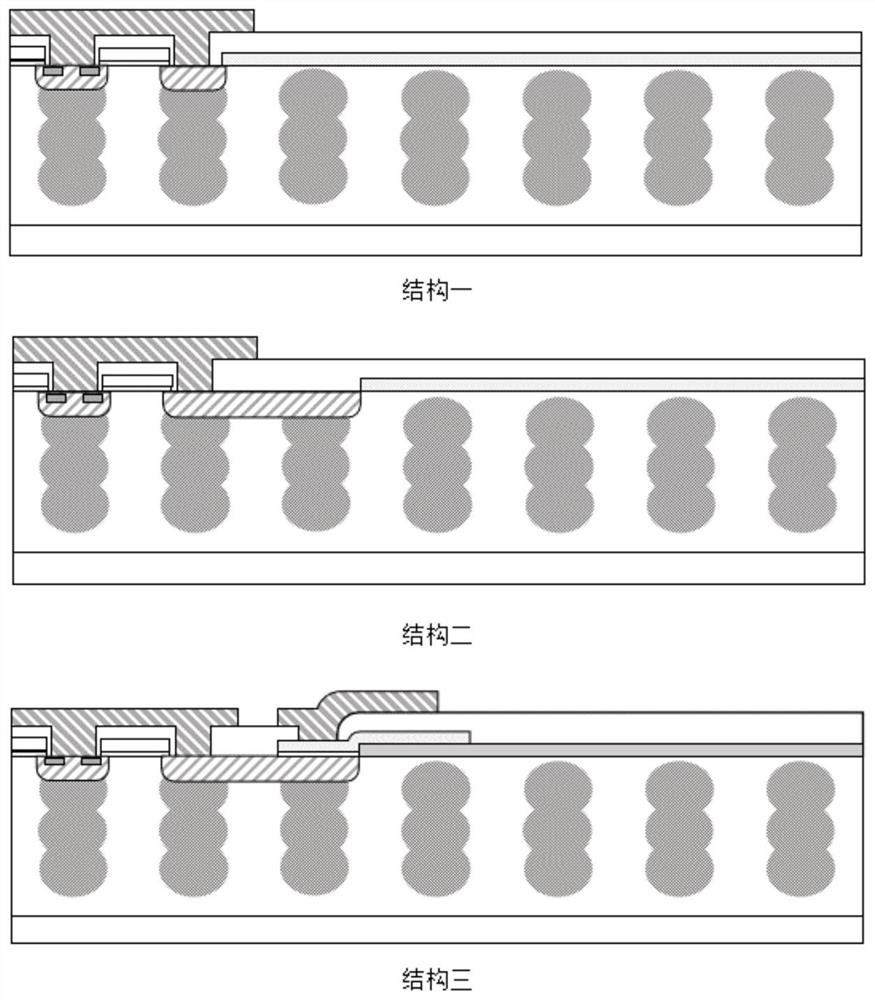

[0042] The invention provides an intelligent super junction MOS device, such as figure 1 and 2 As shown, it includes the main MOS and several functional MOSs integrated and connected on one chip, and the functional MOSs include sampling MOSs and / or startup MOSs.

[0043] The distribution of the main MOS on the chip includes the main MOS terminal area 2 and the main MOS active area 1 set inside the main MOS terminal area 2; the functional MOS is set within the scope of the main MOS active area 1, and the main MOS terminal area 2 and The main MOS active region 1 respectively includes several groups of P-type doped region pillars and N-type doped region pillars arranged in parallel and spaced apart;

[0044] Several functional MOSs are arranged adjacent to each other, and the distribution of functional MOSs on the chip includes functional MOS isolation region...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More