Data storage processing method and device for iterative decoder

A technology for data storage and processing methods, applied in digital transmission systems, forward error control use, electrical components, etc., can solve the problems of full ping-pong RAM, reduced probability of successful decoding, large delay, etc., to save storage space , the storage structure is simple and easy to expand

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

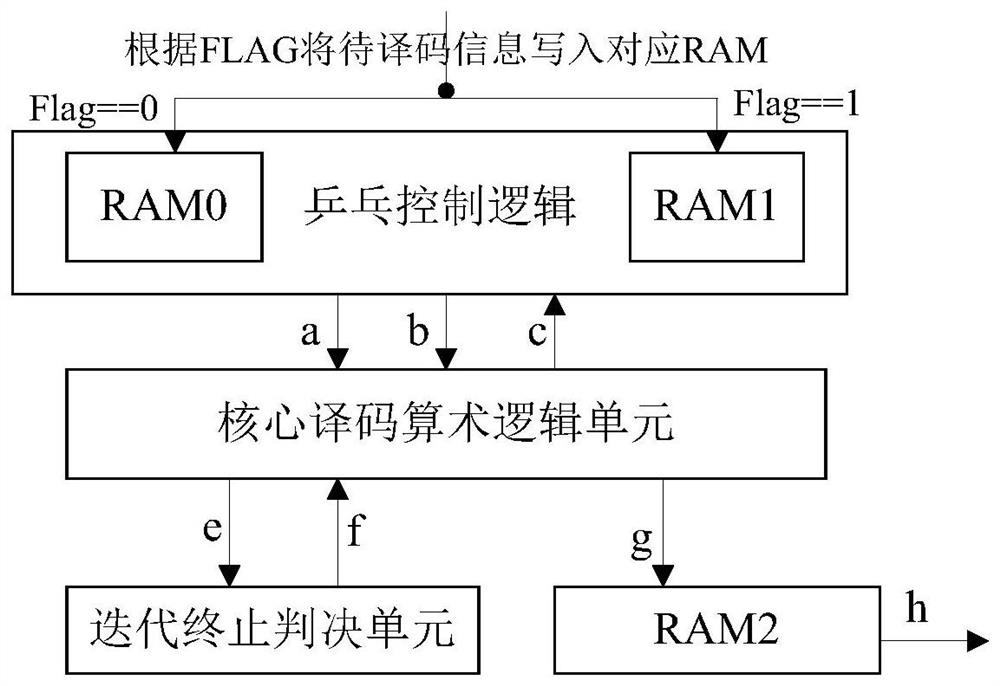

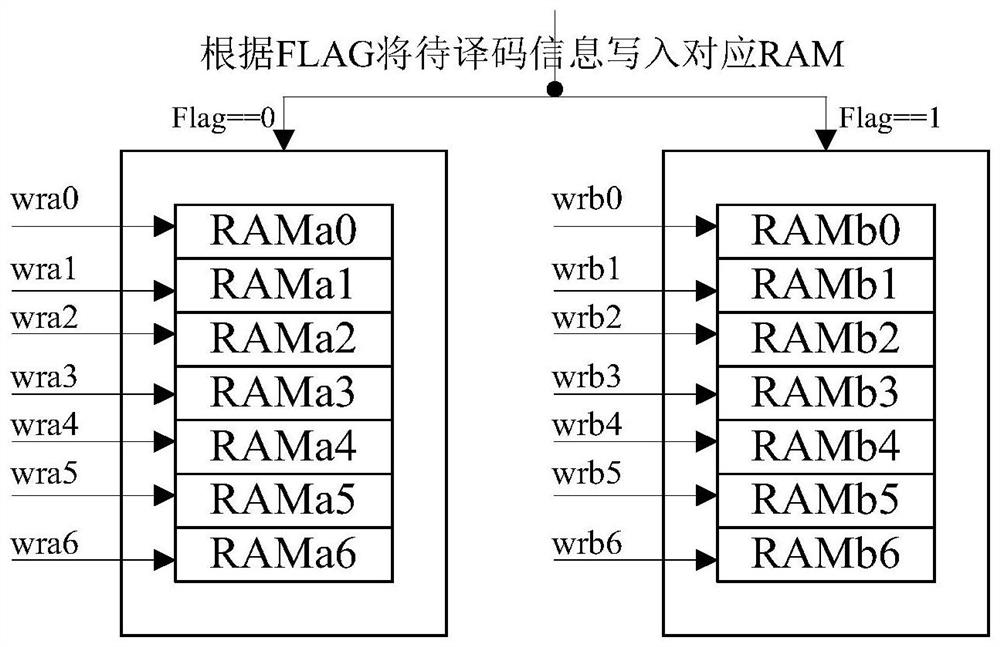

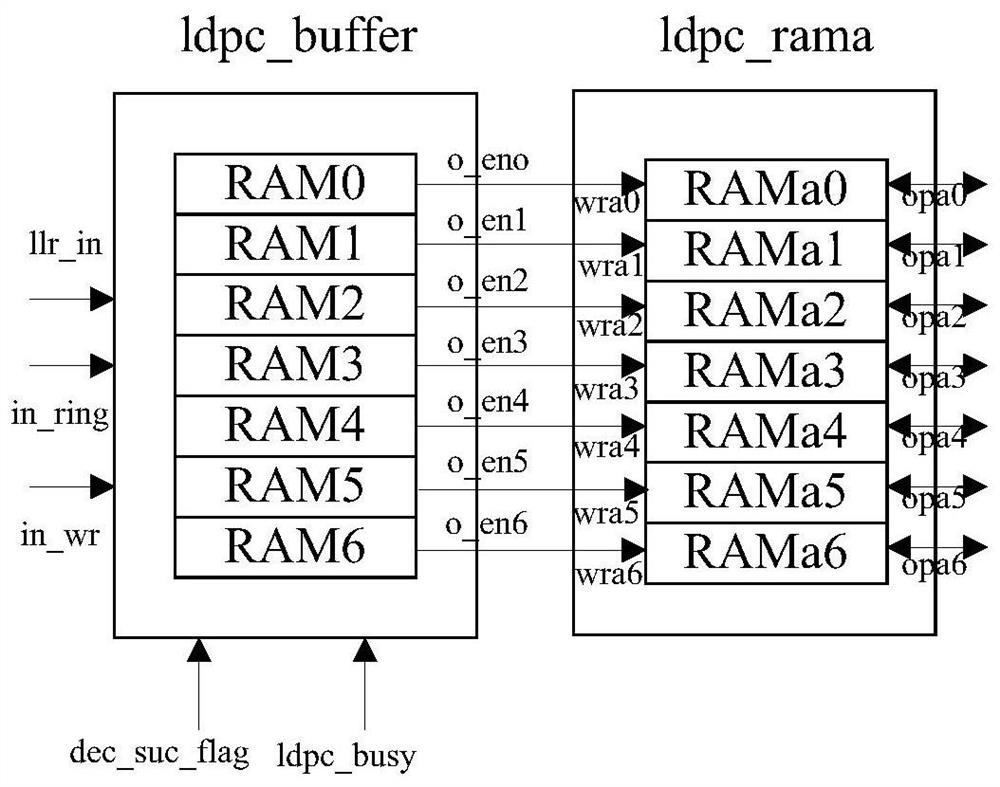

[0078] image 3 It is a schematic diagram of the easy-to-extend storage structure adopted by the LDPC decoder in Example 1 of the present invention. Such as image 3 As shown, the data processing flow of the LDPC decoder is as follows:

[0079] S301, during initialization, the data to be decoded is first written into the buffer ldpc_buffer, which is composed of 7 sub-RAMs, because the data of this RAM is only temporarily stored, so it does not need to participate in mathematical operations, and each point of it is For the original data, one sign bit plus five value bits represent a point, so each sub-RAM is 64X6*16. Since each row can save 32 bits, the sub-RAM depth is increased to 64 with the same capacity.

[0080] S302, ldpc_buffer uses in_wr, in_ring[6:0] to control which sub-RAM to write into. When the data to be decoded that reaches the number of cyclic sub-matrix T is written into ldpc_buffer, the write address will increase by one unit, and the ldpc_buffer has alrea...

Embodiment 2

[0112] 802.11n / ac / ax is currently the most popular indoor LAN solution. This protocol also uses LDPC encoding. The following uses LDPC in the WIFI protocol to illustrate this technical solution. The same solution is not only applicable to this protocol.

[0113] The main parameters of LDPC in the WIFI protocol are code length (N), code rate (R), and cyclic sub-matrix size (T). There are some differences between these parameters and EUHT's LDPC, mainly in that the size T of the cyclic sub-matrix does not have a multiple relationship between the maximum code length and the secondary code length. In order to facilitate hardware implementation, each data to be decoded is represented by 5 bits, and the sign bit is extended to 3 bits. Then the selection scheme of each storage unit of 802.11AC is as follows in Table 5:

[0114] Table 5 802.11AC LDPC encoding parameters and storage unit information

[0115]

[0116] It can be seen from Table 5 that the LDPC in the WIFI protocol h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More