System and method for accelerating MMU mapping table deployment

A mapping table and deployment device technology, applied in the field of SOC chip verification and testing, can solve problems such as MMU configuration errors, incorrect verification results, and long startup time, so as to reduce the probability of configuration errors, accelerate the simulation verification process, and accelerate the simulation running speed. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

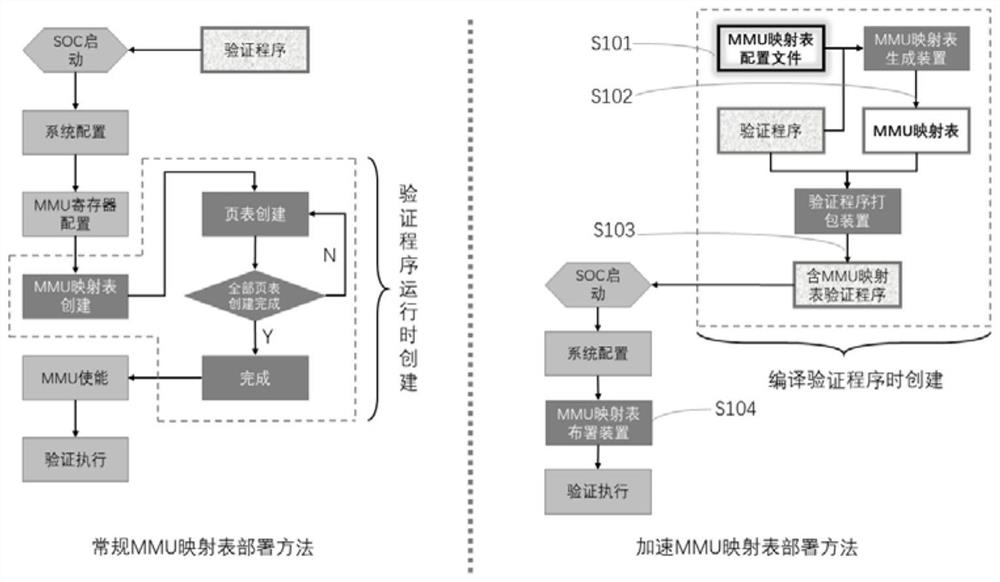

[0039] figure 1 It is a flowchart of a method for accelerating deployment of an MMU mapping table in this embodiment and a flowchart of a method for deploying an existing conventional MMU mapping table. Such as figure 1 The flow of the accelerated MMU mapping table deployment method shown in the right half is as follows:

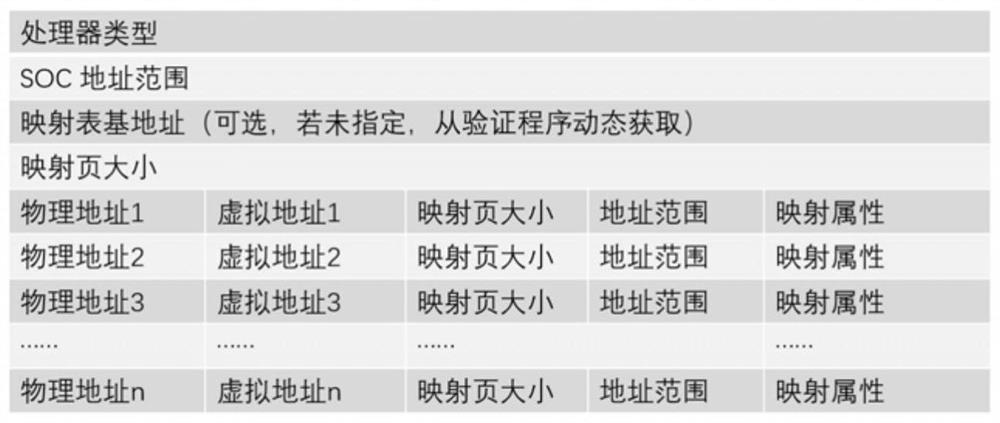

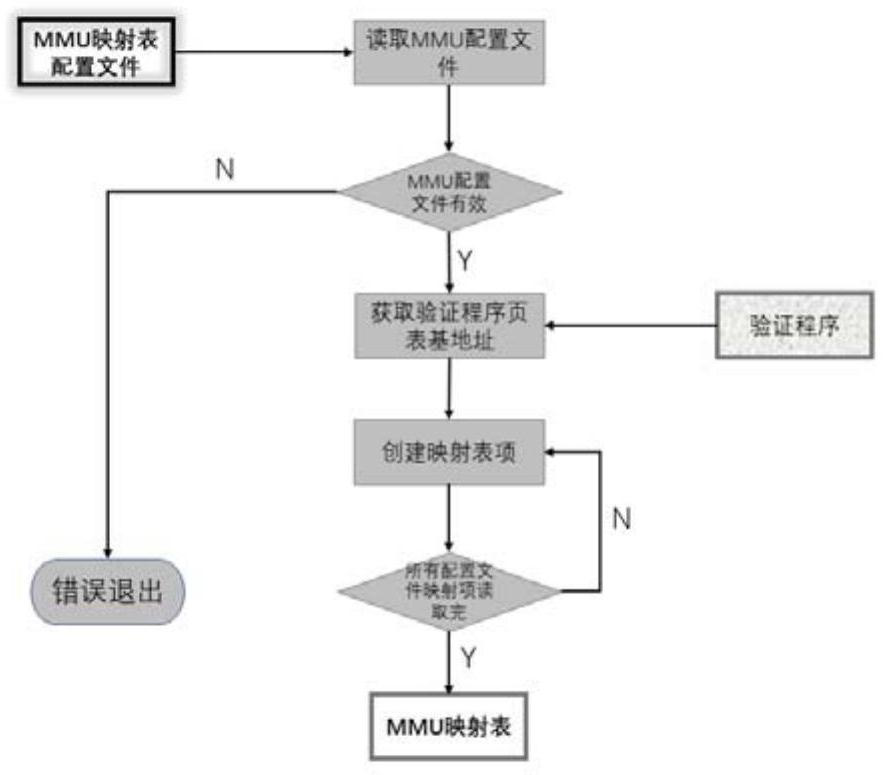

[0040] In step S101, the verifier modifies or creates the MMU mapping table configuration file according to the needs of the current verification program, as the input file of the MMU mapping table generating device; wherein, the main configuration item is the mapping configuration information from phys...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More