Optical module

An optical module and MOS tube technology, applied in the field of optical communication, can solve the problems of pulling down the I2C signal line, pulling down the I2C signal, affecting the normal communication of other module products, etc., so as to ensure normal communication and avoid the level being pulled down. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

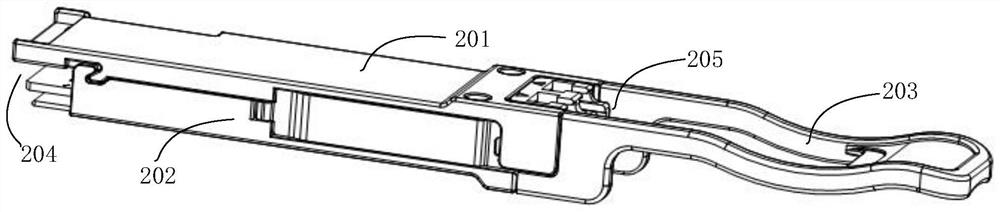

[0028] The technical solutions in some embodiments of the present disclosure will be clearly and completely described below in conjunction with the accompanying drawings. Apparently, the described embodiments are only some of the embodiments of the present disclosure, not all of them. All other embodiments obtained by persons of ordinary skill in the art based on the embodiments provided in the present disclosure belong to the protection scope of the present disclosure.

[0029] Throughout the specification and claims, unless the context requires otherwise, the term "comprise" and other forms such as the third person singular "comprises" and the present participle "comprising" are used Interpreted as the meaning of openness and inclusion, that is, "including, but not limited to". In the description of the specification, the terms "one embodiment", "some embodiments", "exemplary embodiments", "example", "specific examples" example)" or "some examples" and the like are intended...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com