Soft constraint enabling control method based on System verilog

A control method and soft constraint technology, applied in software reuse, faulty computer hardware detection, creation/generation of source code, etc., can solve the difficulty of test code reuse, tape-out failure of major functions, and the trouble of chip function convergence, etc. problems, to achieve the effect of improving fast computing capabilities, ensuring random distribution, and solving random value anomalies

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

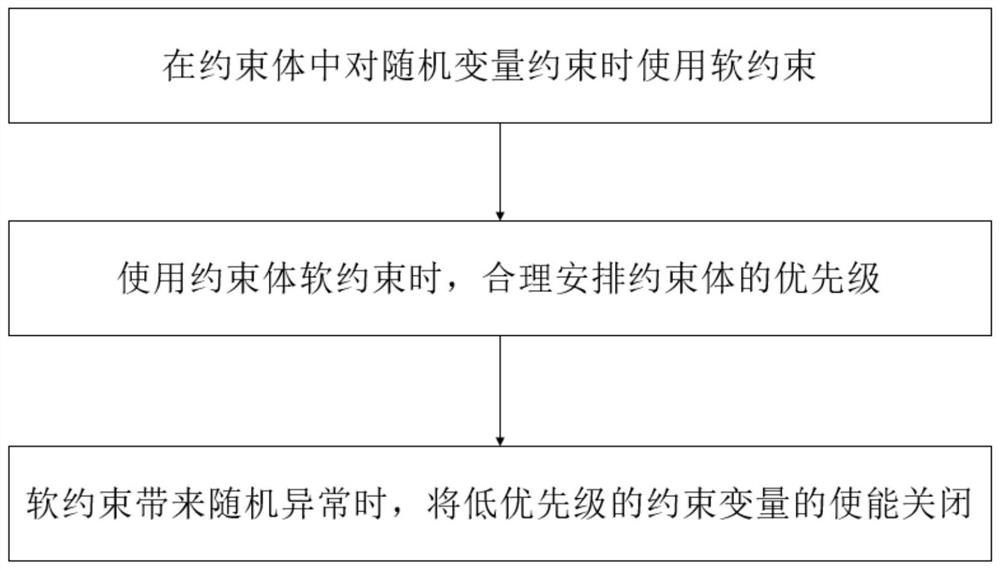

[0020] Such as figure 1 As shown, the present invention discloses a soft constraint enabling control method based on System verilog, comprising the following steps:

[0021] 1) Use soft constraints when constraining random variables in the constraint body;

[0022] 2) When using constraint body soft constraints, reasonably arrange the priority of the constraint body;

[0023] 3) When soft constraints bring random exceptions, disable the low-priority constraint variables. The constraint body is a set of relational expressions used to determine the range of variable values, and the value of the relational expressions is always true.

[0024] Before using soft constraints correctly, you must first understand the differences between soft constraints and hard constraints. If many hard constraints are used in the test code, it is very likely that the solution of the System Verilog constraint solver will be abnormal. That is, if the variables of the constraint body are contradict...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More