Multi-FPGA (Field Programmable Gate Array) system online updating method and system and computer equipment

An update method and technology for updating data, applied in energy-saving computing, climate sustainability, software deployment, etc., can solve the problems of slow update speed and long loading time, avoid conflicts, improve execution efficiency, and reduce the time required for loading Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

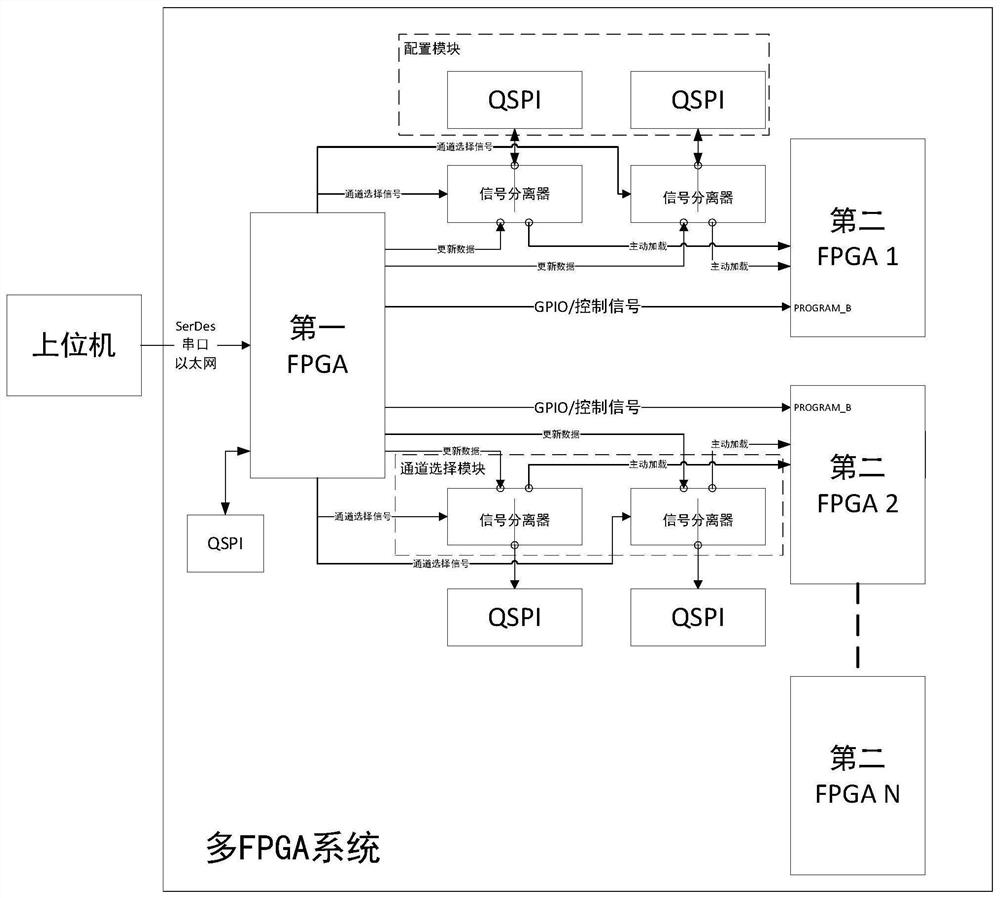

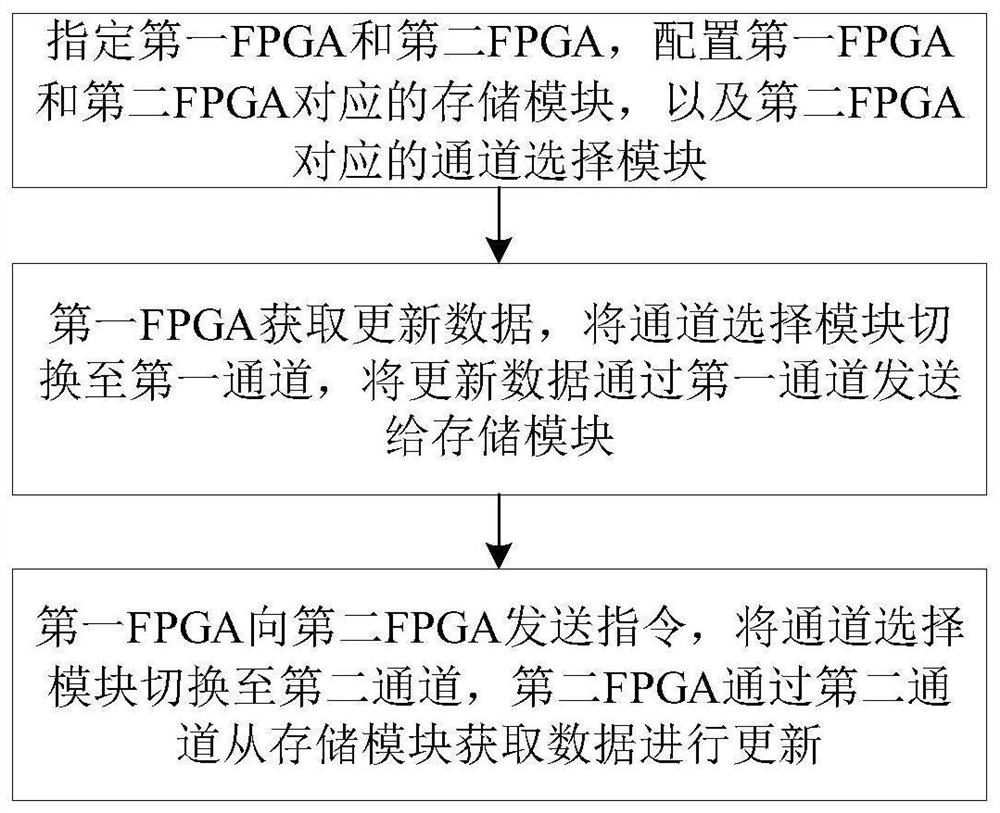

[0036]In order to solve the problems existing in the prior art, this embodiment first proposes a multi-FPGA system, such as figure 1 As shown, the multi-FPGA system in this embodiment includes at least two FPGAs, and also includes a channel selection module and a storage module. The second FPGA in the FPGA is connected through the corresponding channel selection module and the corresponding storage module, respectively. An FPGA is also connected to a storage module corresponding to each second FPGA through a channel selection module corresponding to each second FPGA, the first FPGA is connected to the reload-related pins of the second FPGA through GPIO, and the multi-FPGA system is also connected to an external connection to the host computer.

[0037] In the multi-FPGA system of this embodiment, the first FPGA does not have a channel selection module, but only has a corresponding storage module. The second FPGA is provided with a corresponding channel selection module and a s...

Embodiment 2

[0062] This embodiment is basically the same as the first embodiment, except that in the online update method for a multi-FPGA system in this embodiment, after the first FPGA switches the channel selection module corresponding to the second FPGA to the first channel, the data verification process includes: :

[0063] The first FPGA acquires the current frame of the updated data, and verifies the data of the current frame. If the verification is successful, the data of the current frame is cached in the DDR of the first FPGA. If the verification is unsuccessful, the current frame is discarded. request to resend the data of the current frame, and wait for the data of the current frame; after all frame verification of the updated data is completed, the first FPGA sends the cached data in the DDR to the storage module corresponding to the second FPGA through the first channel . Compared with the first embodiment, the speed of data verification in this embodiment is faster.

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More