Web-based chip testing and debugging system

A debugging system and chip testing technology, which is applied in error detection/correction, instrumentation, computing, etc., can solve the problems that chip testing and debugging systems cannot realize remote debugging, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described below with reference to the accompanying drawings and embodiments.

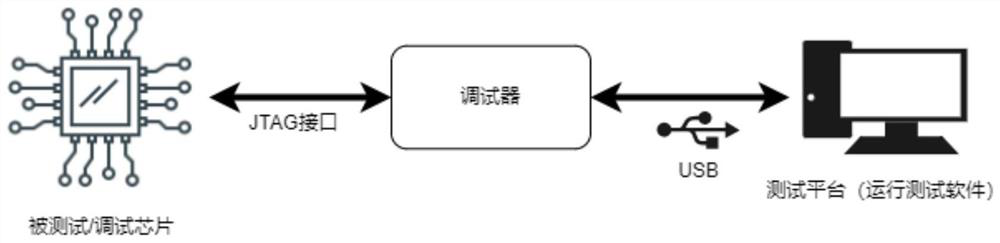

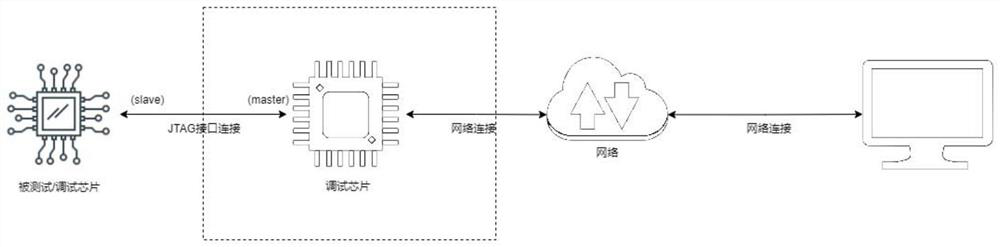

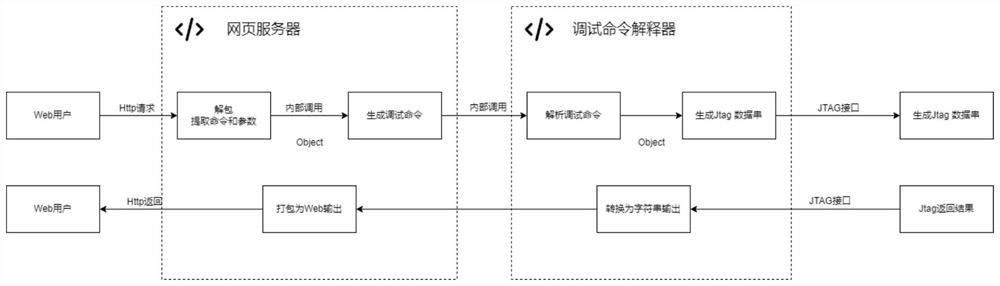

[0027] figure 2 is the Web-based chip testing and debugging system architecture in the embodiment of the present invention; image 3 It is a schematic diagram of data exchange of a Web-based chip testing and debugging system in an embodiment of the present invention.

[0028] See figure 2 and image 3 , The Web-based chip testing and debugging system of the embodiment of the present invention includes a debugging chip, the debugging chip is connected to the tested chip, the debugging chip is connected to a web browser through a network, and the Http request is sent to the debugging chip through the Web browser; the debugging chip receives Parse the Http request sent by the web browser, the debug chip parses the Http request and converts it into a JTAG command and sends it to the chip under test, the chip under test executes the JTAG command and retur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More