Integrated circuit with embedded memory module

A technology for memory modules and integrated circuits, applied in static memory, instruments, measurement circuits, etc., can solve problems such as reducing IC performance and affecting the function of scan test timing paths, reducing the number of switching times and avoiding power problems.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

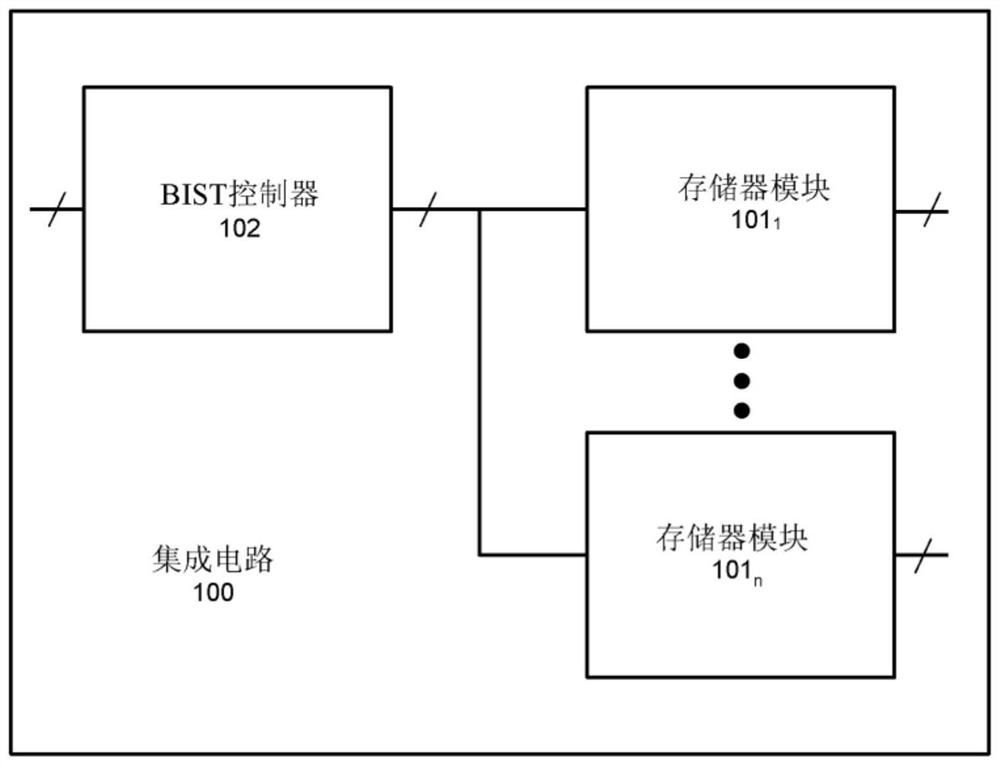

[0033] figure 1 Shown with multiple memory modules 101 1-n An example integrated circuit (IC) 100 . not for clarity figure 1 Other components shown in can also be present in IC 100 . Memory module 101 1-n The operation of each of the built-in self-test operations is controlled by the BIST controller 102, which reports to each memory module 101 1-n A signal is provided to deactivate normal operation and actually cause it to operate under the control of the BIST controller 102 .

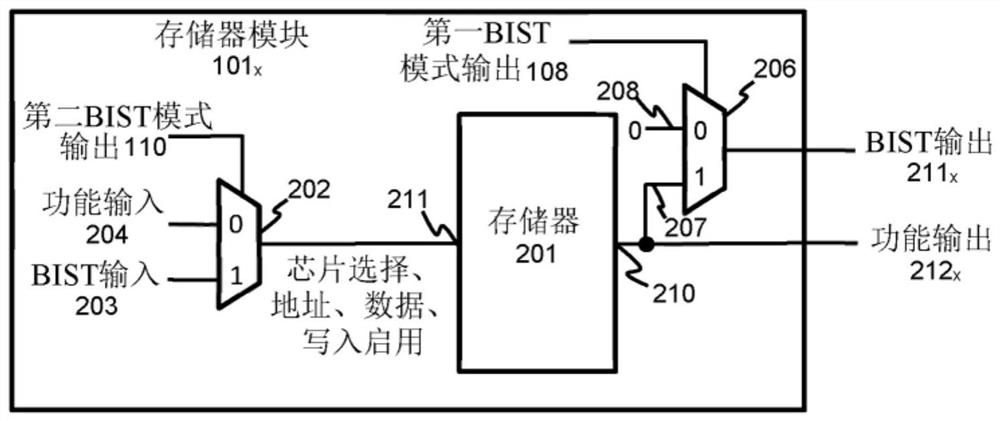

[0034] figure 2 Additional details of an example BIST controller 102 are shown. The BIST controller 102 includes: a scan enable input 106 for enabling scan shift operations; a BIST control input 105 for enabling BIST operations; a BIST mode input 109 for determining the BIST mode to be employed; Multiplexer 103 1-n BIST input for each of the 104 1-n . Each multiplexer 103 1-n Includes a pair of inputs that can be accessed by selecting input 115 1-n Enter 104 in multiple BISTs 1-n The pair...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More