Test terminal negation circuit

A technology for testing terminals and circuits, applied in circuits, measuring electricity, measuring electrical variables, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

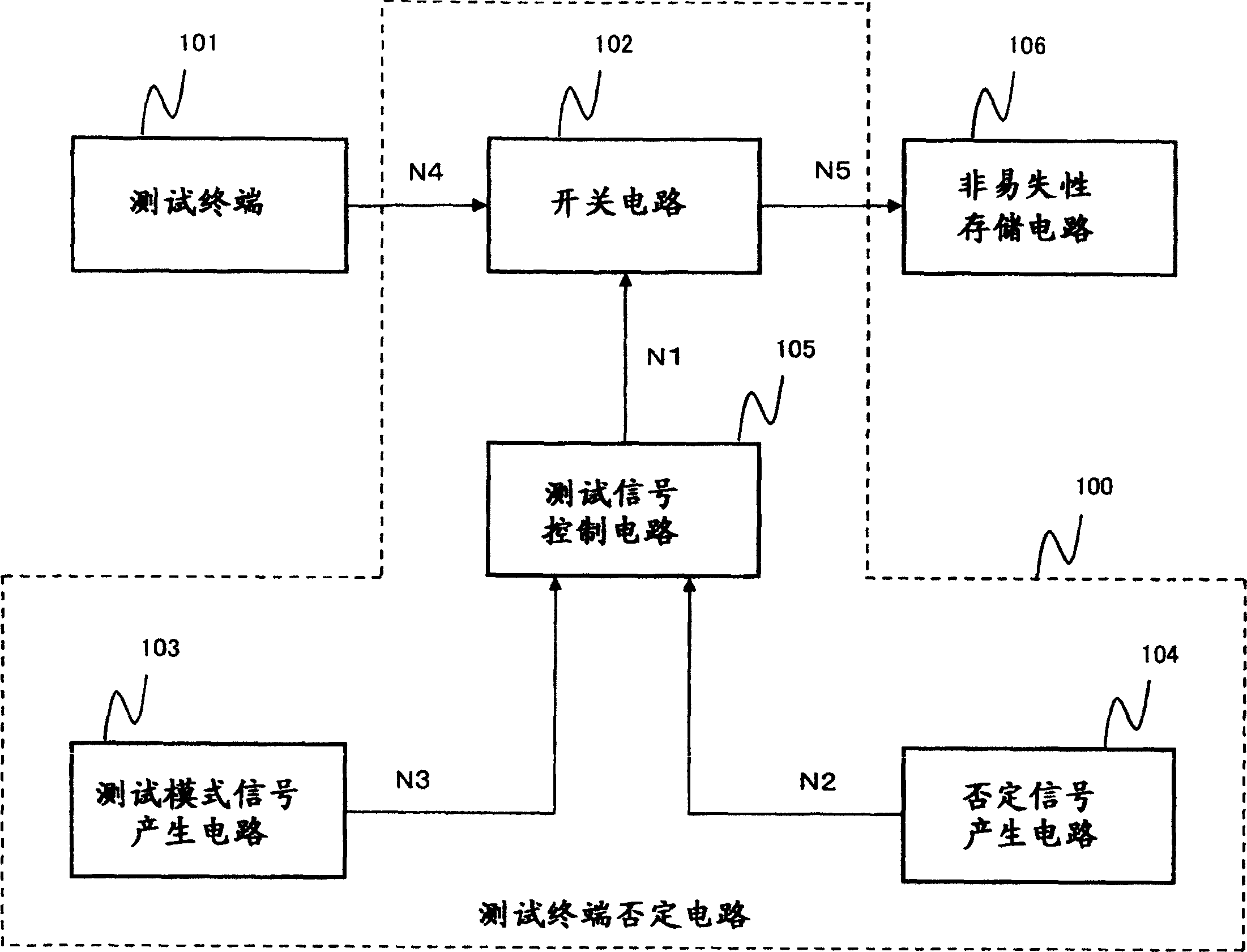

[0019] Embodiments of the present invention will be described with reference to the drawings. figure 1 is a circuit diagram showing an embodiment of a test terminal negation circuit according to the present invention (hereinafter sometimes referred to as "circuit of the present invention"). Such as figure 1 As shown in , the circuit 100 of the present invention includes a switch circuit 102 , a test mode signal generation circuit 103 , a negative signal generation circuit 104 , and a test signal control circuit 105 .

[0020] The switch circuit 102 receives the test signal from the test terminal 101 and relies on the level of the output node N1 of the test signal control circuit 105 to output it to the non-volatile storage circuit 106 in its affirmed state or a predetermined negated state , the nonvolatile storage circuit 106 is the object circuit to be tested. For example, the switching circuit 102 includes a CMOS transmission gate or the like.

[0021] The test mode signa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More