Semiconductor integrated device

一种集成器件、半导体的技术,应用在半导体集成器件领域,能够解决很难形成接触等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

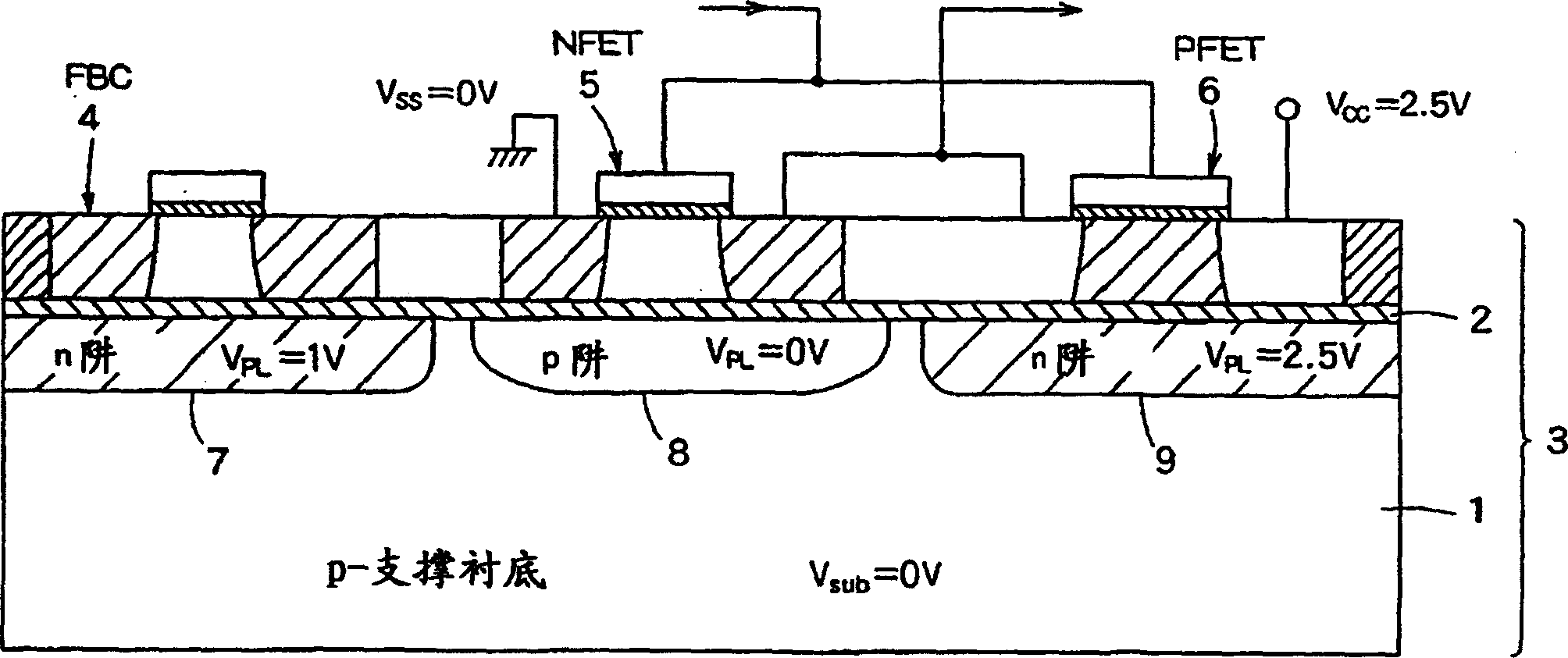

[0062] figure 1 is a sectional view of the semiconductor integrated device according to the first embodiment of the present invention. exist figure 1 In the semiconductor integrated device of , a cross-sectional structure of a peripheral circuit of a semiconductor memory device using FBCs as a memory element is shown.

[0063] In the present embodiment, SOI substrate 3 including p-type support substrate 1 and buried oxide film 2 formed as a thin film is used. By forming the buried oxide film 2 as a thin film, the signal quantity of FBCs can be sufficiently secured, and the data retention time can be extended.

[0064] figure 1 In the SOI substrate 3, the FBC4, the NFET 5, and the PFET 6 are formed on the upper surface of the buried oxide film 2 so as to be separated from each other. An n-well diffusion region 7 is formed in p-type supporting substrate 1 under FBC 4 in contact with buried oxide film 2 . A p-well diffusion region 8 is formed in the p-type supporting substra...

no. 2 approach

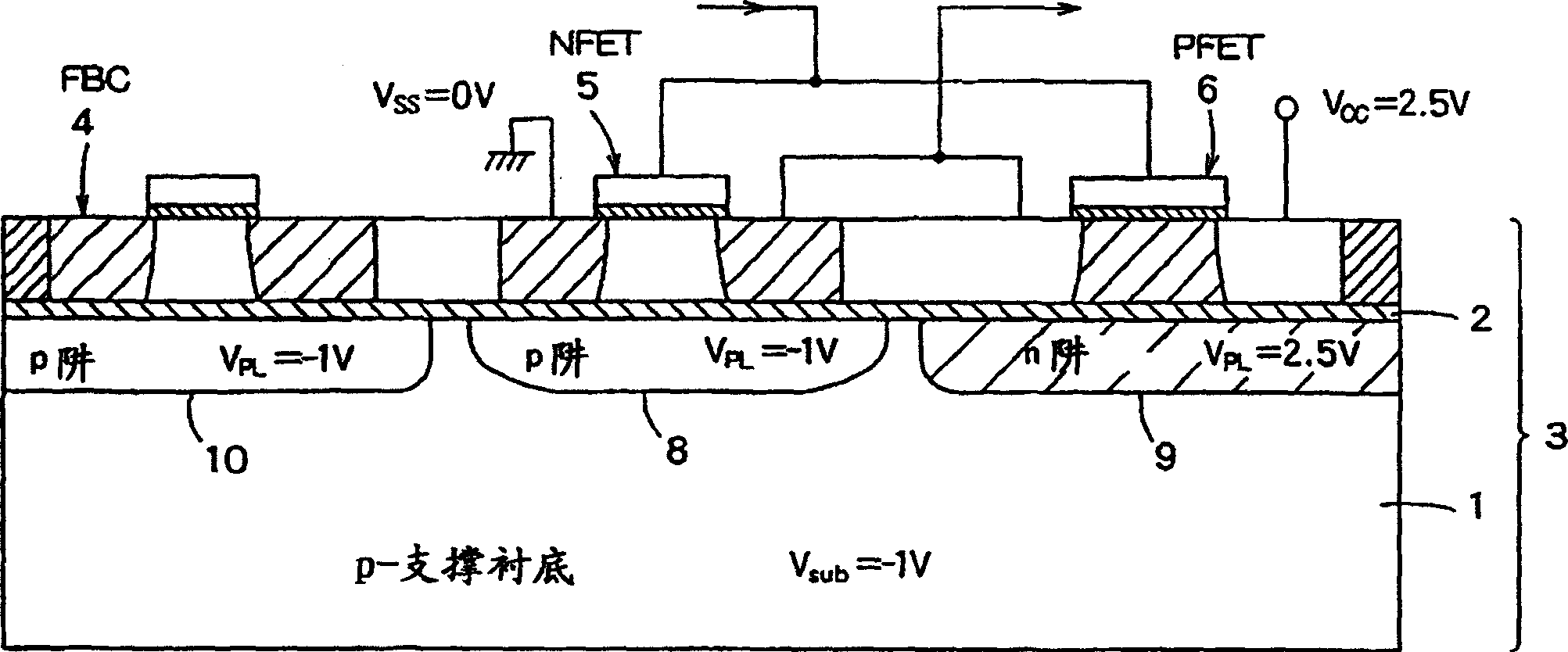

[0073] In the second embodiment, when a voltage lower than 0 V is applied to the p-type supporting substrate 1 of the SOI substrate 3, the reverse channel is prevented from being formed.

[0074] image 3 is a sectional view of a semiconductor integrated device according to a second embodiment of the present invention. follow with figure 1 same way, image 3 The semiconductor integrated device shown includes FBC 4 , NFET 5 and PFET 6 formed on SOI substrate 3 including p-type support substrate 1 and buried oxide film 2 formed as a thin film so as to be separated from each other.

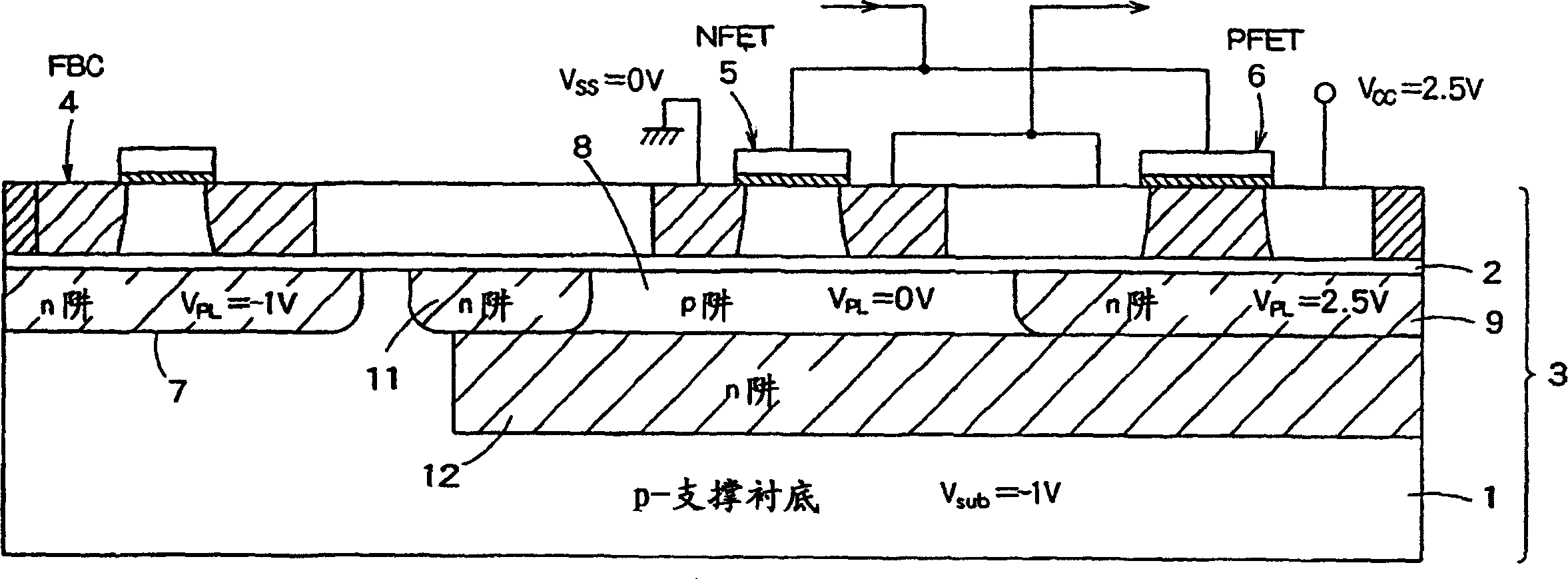

[0075] follow with figure 1 In the same manner, n-well diffusion region 7 is formed in p-type support substrate 1 located below FBC 4 . A p-well diffusion region 8 is formed in the p-type support substrate 1 under the NFET 5 . Furthermore, n-well diffusion region 11 is formed so as to be adjacent to p-well diffusion region 8 . An n-well diffusion region 12 is formed below the lower surfaces of ...

no. 3 approach

[0081] In the first and second embodiments, SOI substrate 3 including p-type support substrate 1 is used. However, an SOI substrate 3 including an n-type support substrate may be used.

[0082] In this case, with figure 1 The corresponding structure becomes as Figure 5 shown. Figure 5 The semiconductor integrated device shown includes an n-well diffusion region formed under the FBC 4, a p-well diffusion region 8 formed under the NFET 5, an n-well diffusion region 9 formed under the PFET 6, and an area between the p-well diffusion region 8 and A p-well diffusion region 13 is formed on the lower surface side of the n-well diffusion region 9 .

[0083] The n-type support substrate 20 is set to a voltage of Vsub=0V. A voltage VPL=0V is applied to the n-well diffusion region 7 . Set the p-well diffusion region 8 to the voltage VPL=0V. A voltage VPL=2.5V is applied to the n-well diffusion region 9 . P-well diffusion region 13 is provided to prevent short circuit between n-w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More