Method of driving liquid crystal display and liquid crystal display

A technology of a liquid crystal display device and a driving method, which is applied to static indicators, nonlinear optics, instruments, etc., can solve the problems of brightness increase, contrast decrease, and the inability to fully ensure the writing time of pixel electrode charge, that is, the charging period, etc. Horizontal line unevenness, the effect of ensuring charging time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

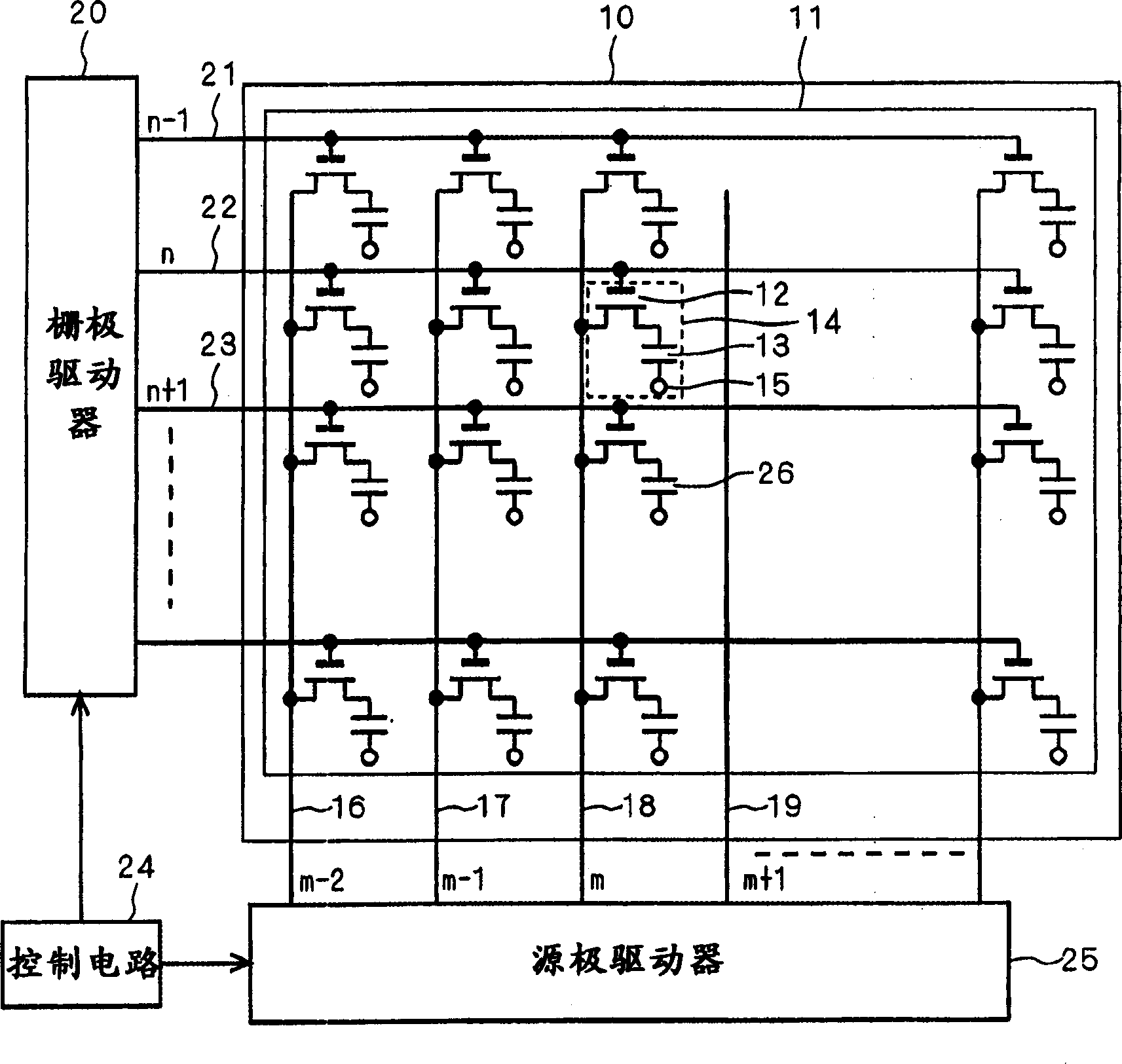

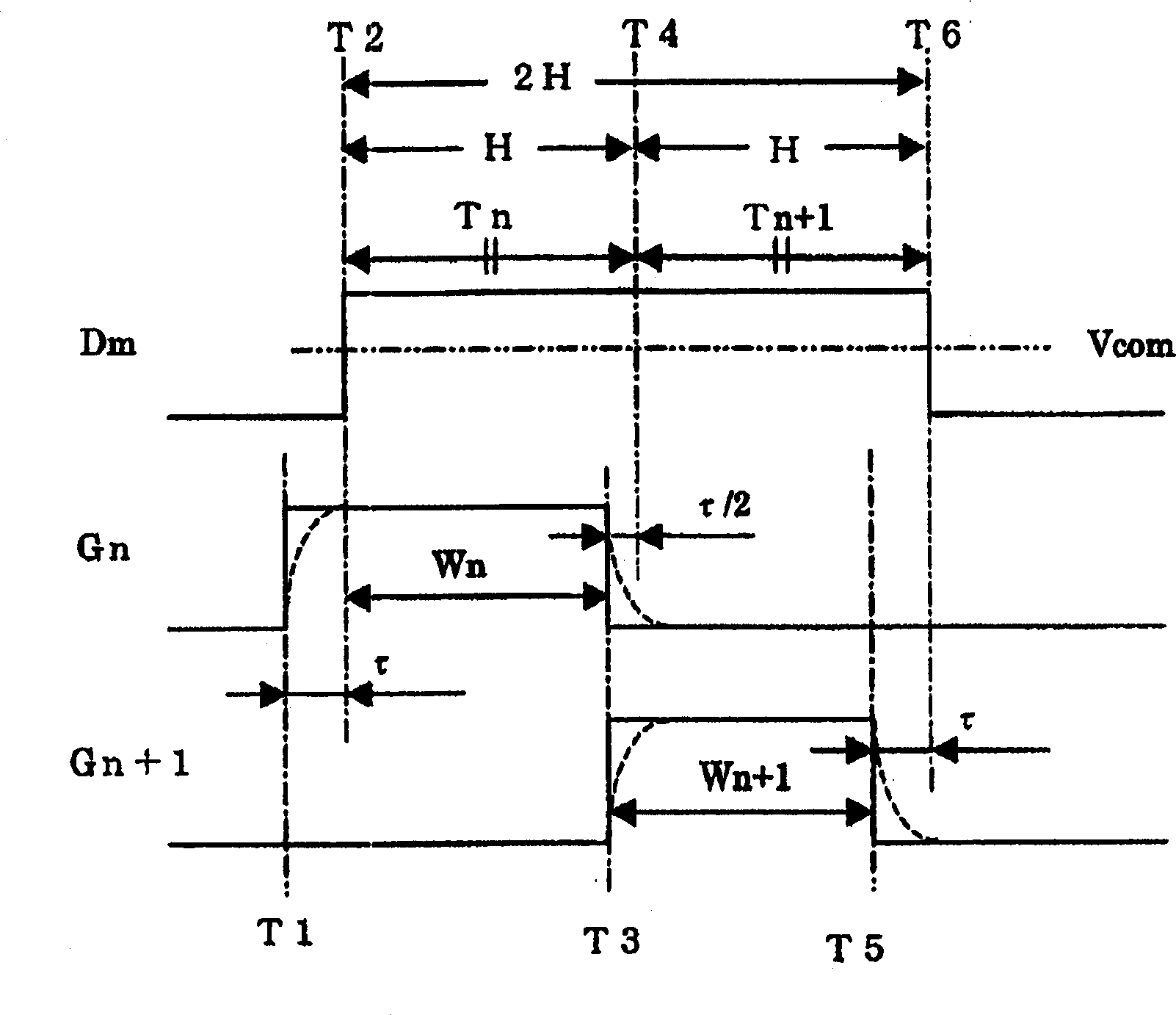

[0016] figure 1 It is a configuration diagram showing a liquid crystal display device controlled by implementing the driving method of Embodiment 1 of the present invention. figure 1 Among them, the always bright liquid crystal panel 10 is composed of a plurality of source wirings 16, 17, 18, 19 crossing each other and a plurality of gate wirings 21, 22, 23 in an active matrix substrate 11 formed in a matrix, and the The counter substrate (not shown) facing the active matrix substrate 11 is pasted with a gap, and a liquid crystal (not shown) is sandwiched between the gap. Here, the pixel portion 14 indicated by a dotted line is arranged at the intersection of the source wirings 18, 19 and the gate wirings 22, 23, a TFT 12 and a pixel electrode 13 are provided as switching elements, and the gate of the TFT 12 is connected to the gate wiring 22. The source is connected to the source wiring 18 , and the drain is connected to the pixel electrode 13 . In addition, the pixel ele...

Embodiment 2

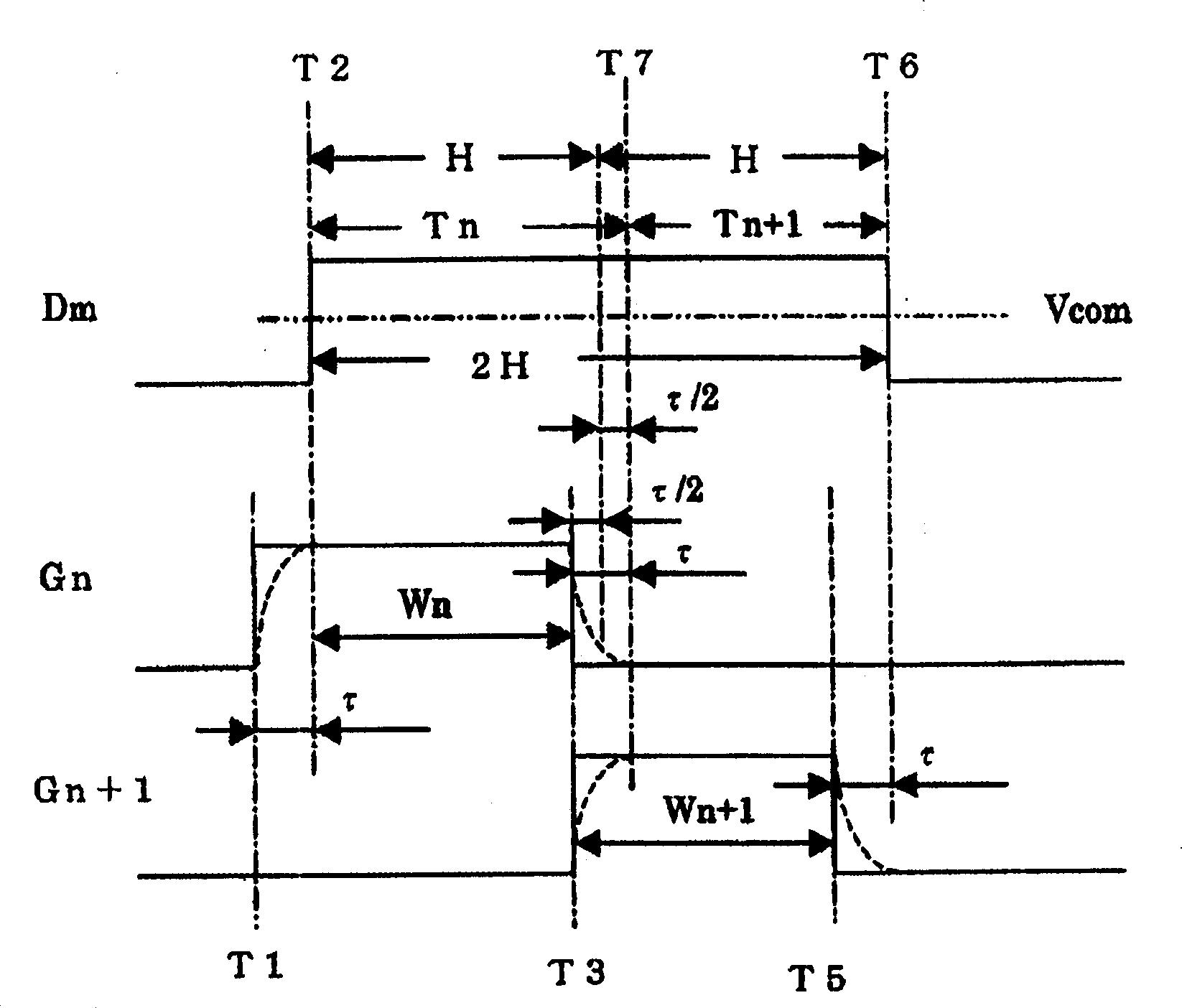

[0027] image 3 It is a timing chart showing a method of driving a liquid crystal display device according to Embodiment 2 of the present invention. In this embodiment 2, the above-mentioned embodiment 1 figure 2 The output switching time of the data signal Dm, that is, the time T4 is delayed by the period τ / 2 to be the time T7, and the period T3-T7, that is, the fourth period is taken as τ. That is, the period T5-T6, that is, the third period and the fourth period T3-T7 are set to have the same length τ. Others are the same as in Embodiment 1, so description is omitted.

[0028] Such as image 3 As shown, the signal output period of the data signal Dm is Tn=H+τ / 2, Tn+1=H−τ / 2. In Embodiment 2, the output switching time T7 of the data signal Dm is set to be delayed by only the period τ from the turning-off time T3 of the gate selection signal Gn as the fourth period. In addition to raster screen display, it is possible to suppress display unevenness caused by slowing down ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More