Cache memory analyzing method

一种缓冲存储器、高速缓冲的技术,应用在存储器系统、内存地址/分配/重定位、仪器等方向,能够解决高速缓冲存储器存取状态不得而知等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

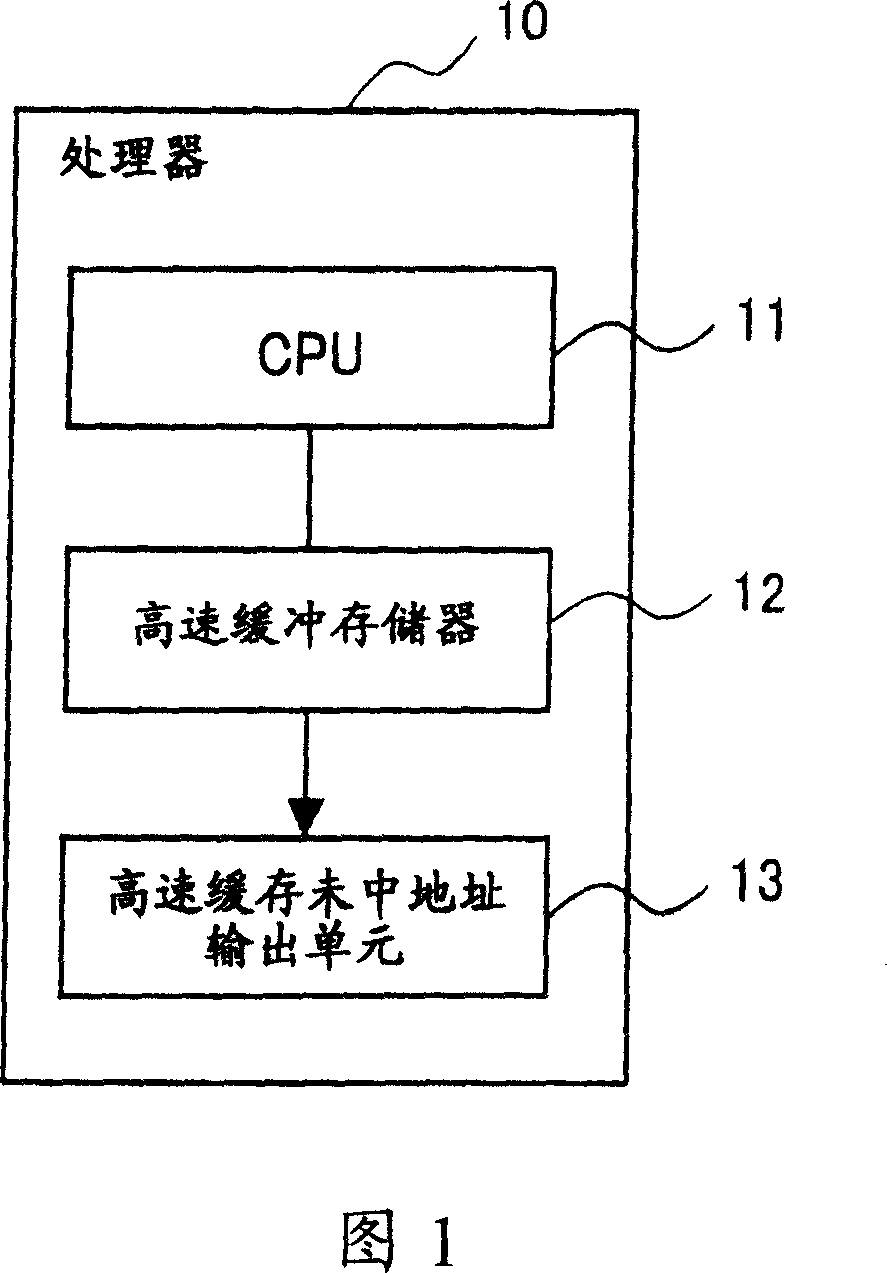

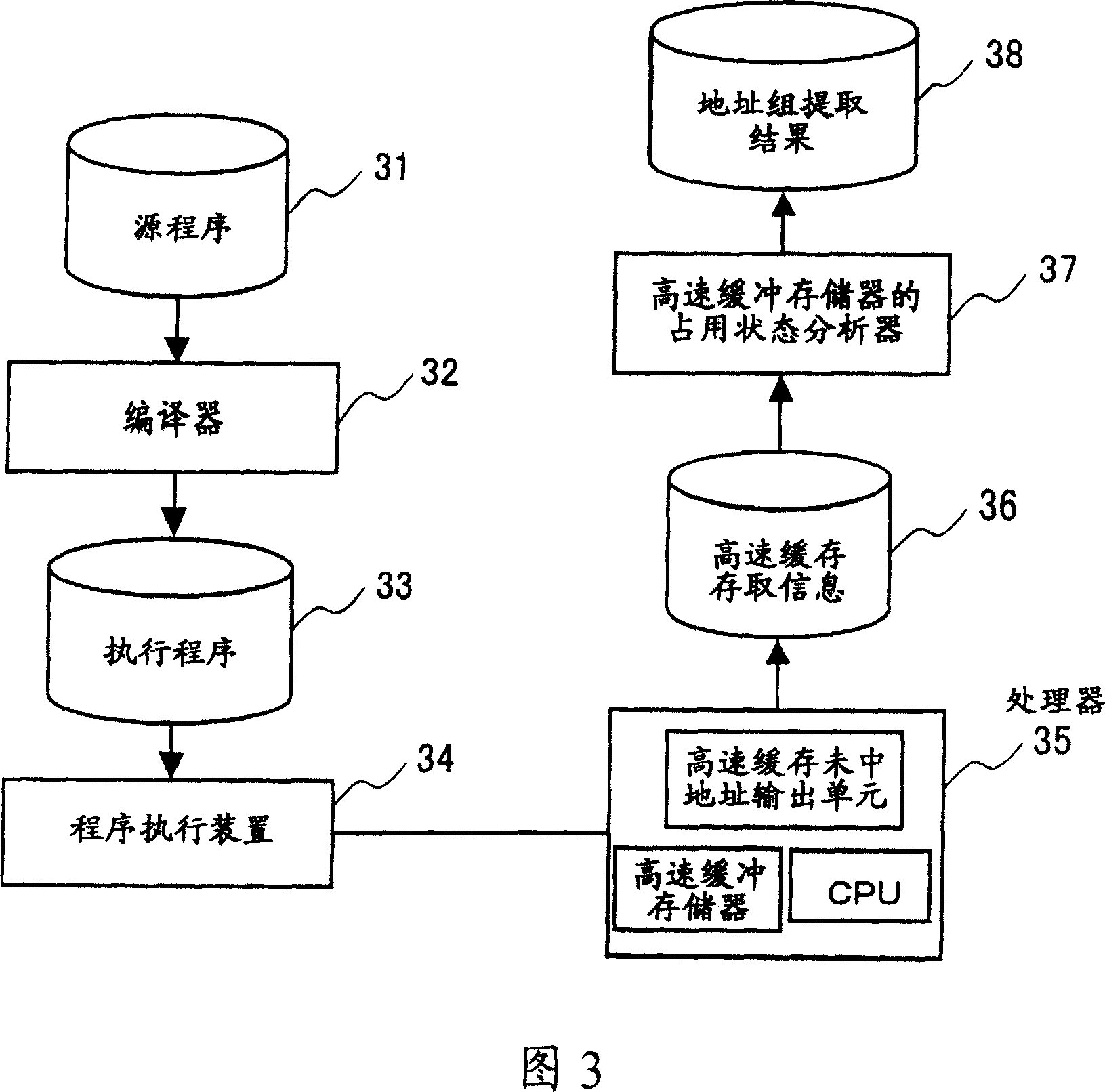

[0053] FIG. 1 is a schematic diagram of a processor 10 and its system for outputting cache access information with cache miss address records according to an embodiment of the present invention.

[0054] In FIG. 1 , a processor 10 includes a CPU 11 , a cache memory 12 and a cache miss address output unit 13 . The cache memory 12 has a structure of a multi-way set associative system. When a cache miss occurs when data is requested from the cache memory 12 , the cache miss address output unit 13 outputs the address of the data where the miss occurred as a cache miss address to the outside of the processor. With the above configuration, the processor 10 can analyze the occupancy state of the cache memory using only the address at which the cache miss occurs.

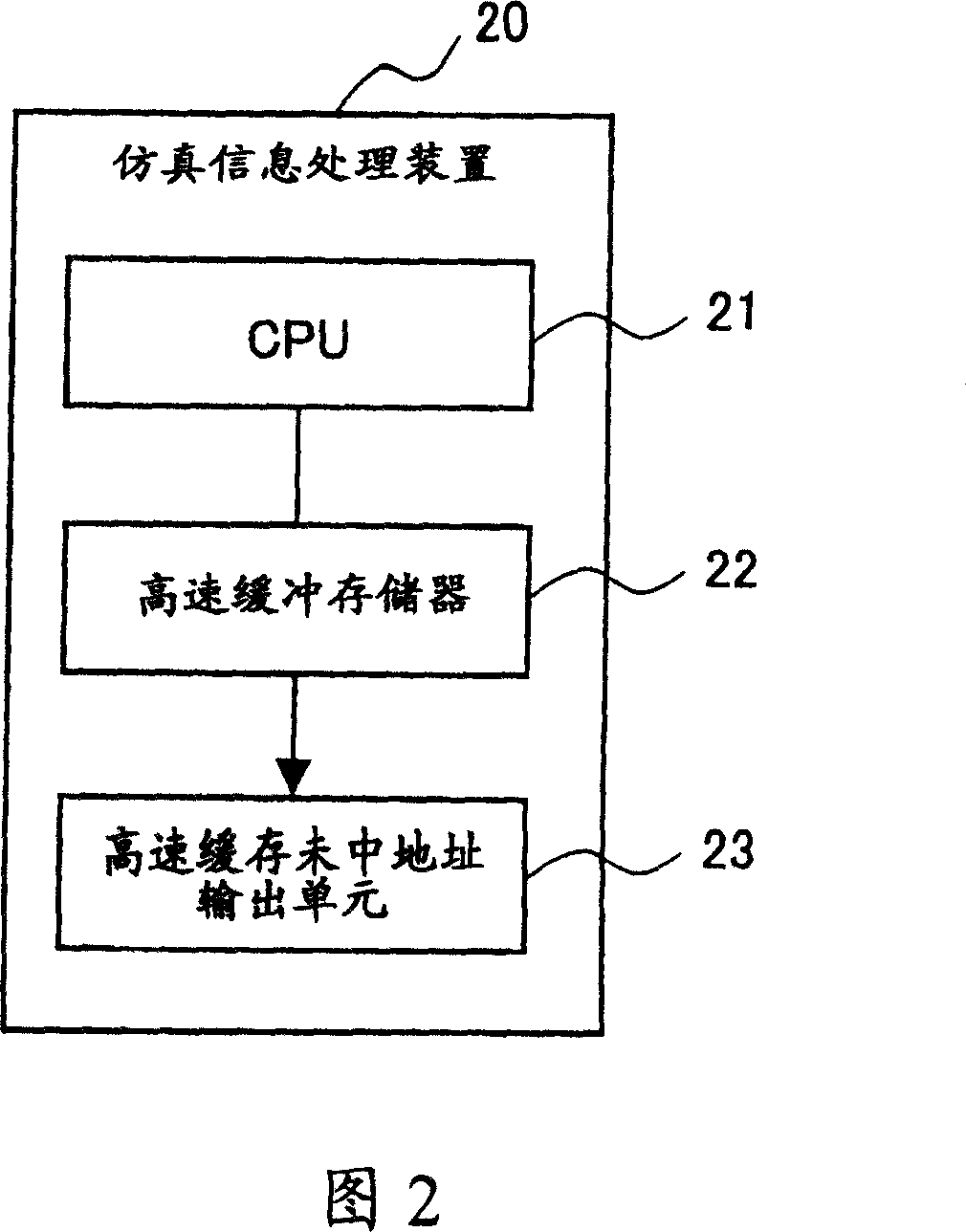

[0055] FIG. 2 shows a simulated information processing device 20 simulating the structure shown in FIG. 1 . The emulation information processing device 20 includes a CPU 21 , a cache memory 22 and a cache miss address out...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More