Wafer level package and method of manufacturing the same

a technology of level package and level package, which is applied in the direction of semiconductor devices, electrical equipment, semiconductor/solid-state device details, etc., can solve the problems of increasing the thickness of the entire molding resin, the need for packaging all chips for a very long time, and the increase of the process cost, so as to reduce the process cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030]Hereinafter, a matter regarding to an operation effect including a technical configuration to achieve the object of a wafer level package and a method of manufacturing the same in accordance with the present invention will be appreciated clearly through the following detailed description with reference to the accompanying drawings illustrating preferable embodiments of the present invention.

[0031]A Structure of a Wafer Level Package

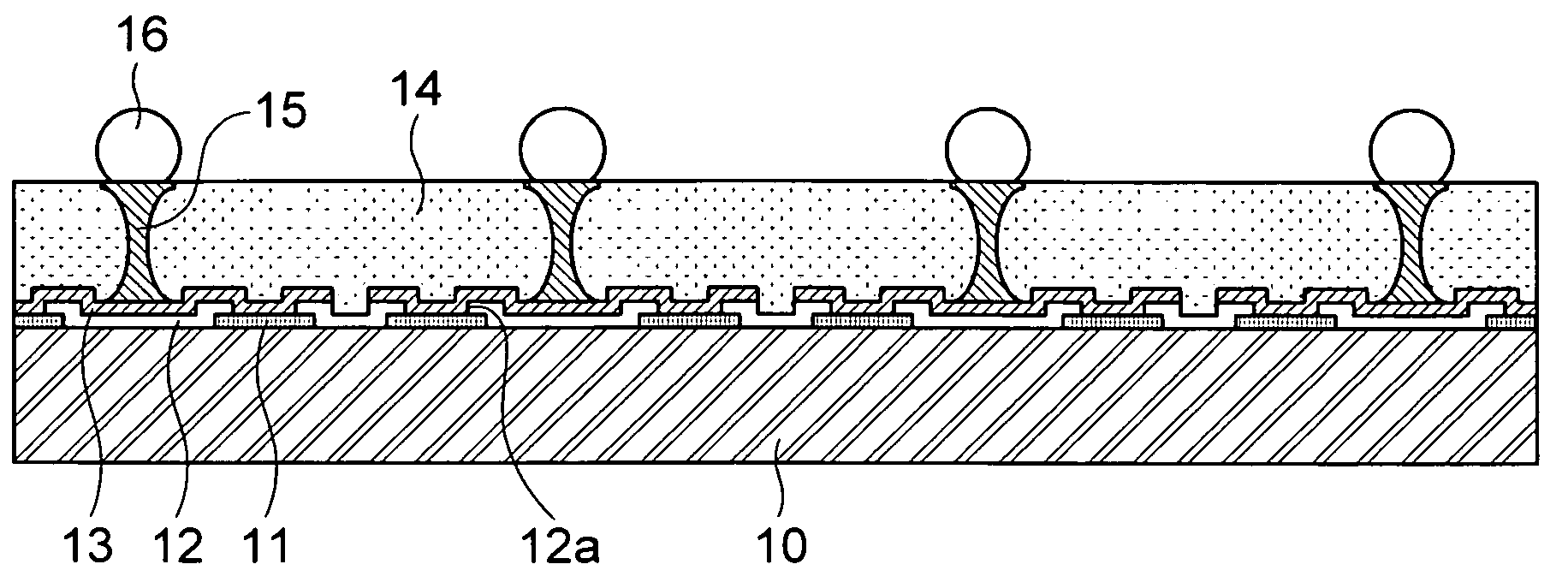

[0032]First of all, a wafer level package in accordance with an embodiment of the present invention will be described in detail with reference to FIG. 1 to FIG. 4.

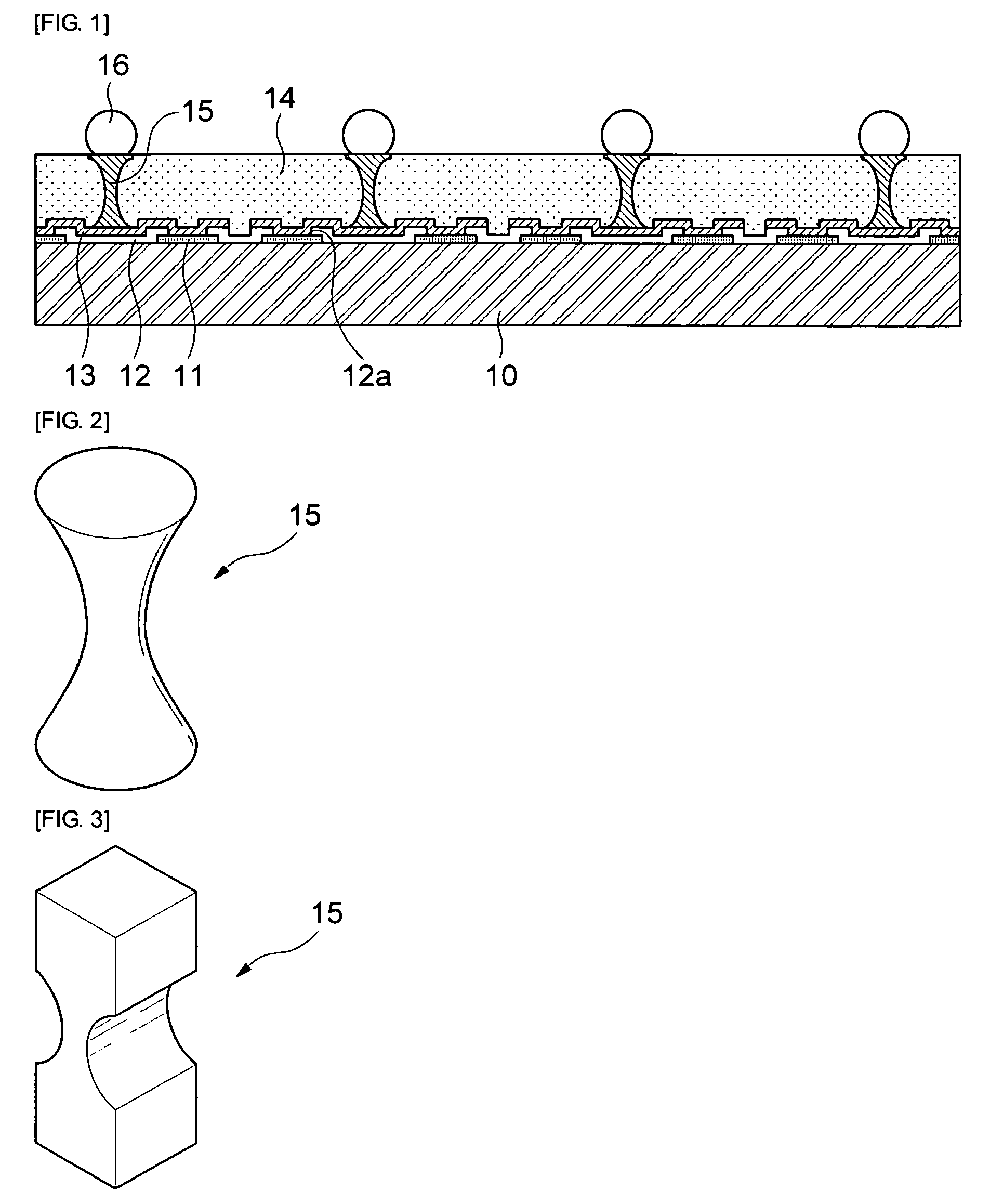

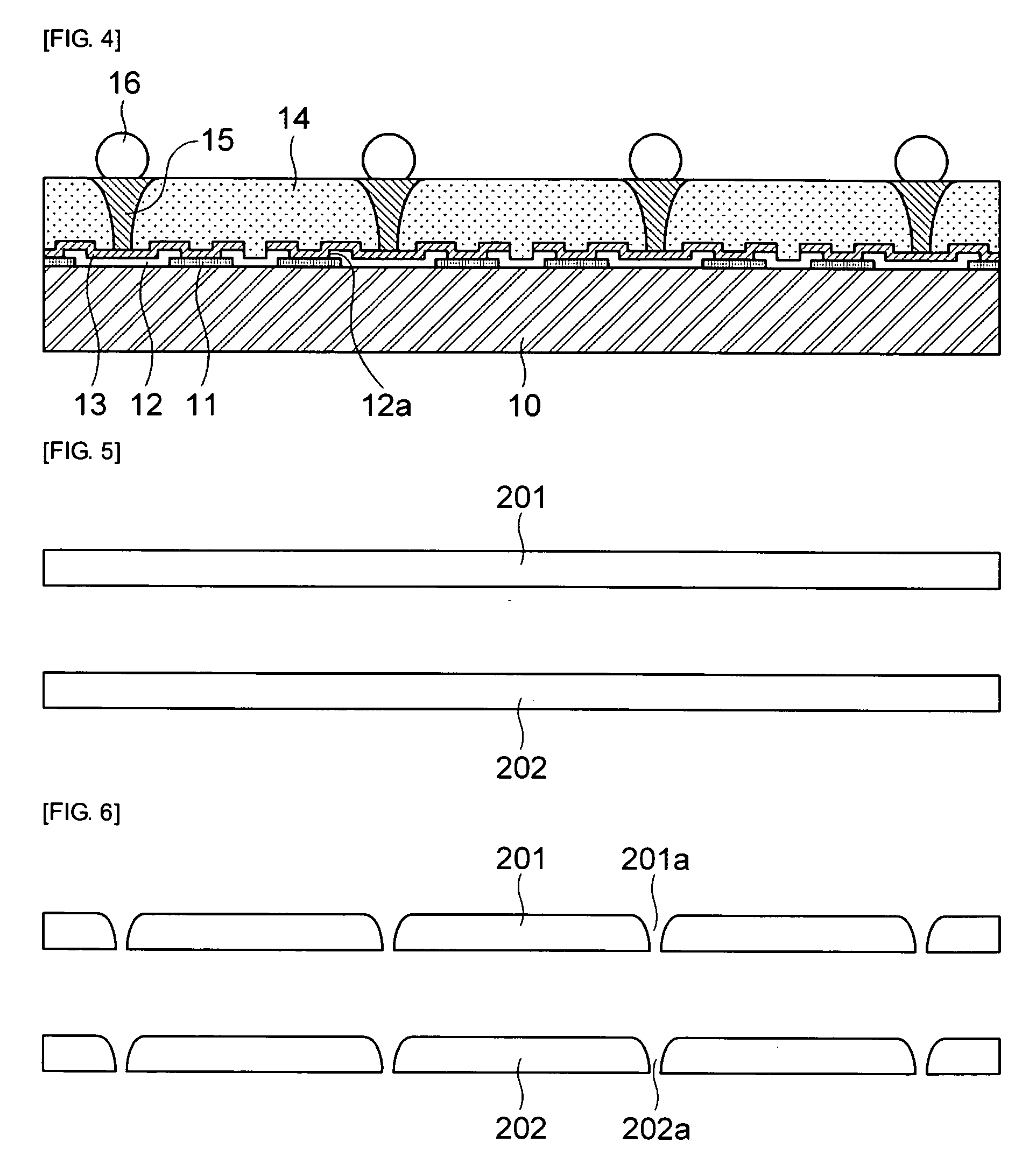

[0033]FIG. 1 is a cross sectional view illustrating a structure of a wafer level package in accordance with an embodiment of the present invention, FIG. 2 and FIG. 3 are perspective views illustrating structures of metal posts in accordance with the embodiment of the present invention, FIG. 4 is a cross sectional view illustrating a structure of a wafer level package in accordance with ano...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More