OpportunistIC placement of IC test strucutres and/or e-beam target pads in areas otherwise used for filler cells, tap cells, decap cells, scribe lines, and/or dummy fill, as well as product IC chips containing same

a technology of e-beam target pads and scribe lines, which is applied in the direction of individual semiconductor device testing, semiconductor/solid-state device testing/measurement, instruments, etc., can solve the problems of limited area available in the scribe line of product wafers, inability to accommodate certain types of test structures, and still less than ideal, so as to improve the coverage of test structures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

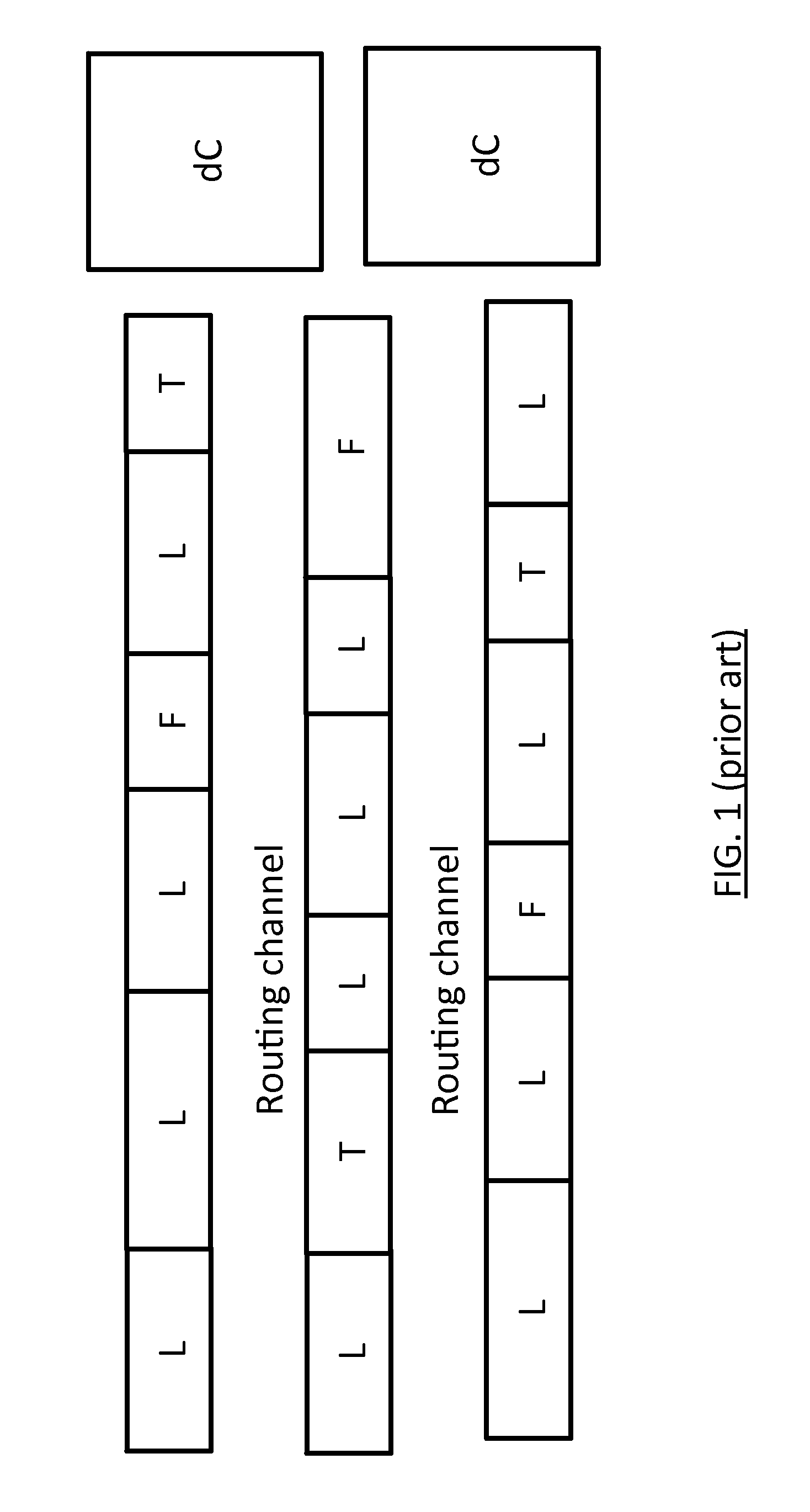

[0136]FIG. 1 conceptually depicts an illustrative section of a prior-art standard cell layout that includes logic cells (L), tap cells (T) and filler cells (F) arranged in rows, with routing channels between the rows, and nearby decap cells (dC). As depicted, the overall distribution of decap, tap and filler cells within this illustrative section is irregular and does not follow any obvious pattern or symmetry. (Persons skilled in the art will immediately recognize that the depictions herein are conceptual, and only intended to illustrate the principles of the invention, rather than represent actual layout realities. Indeed, such skilled artisans will appreciate that tap cells typically come in only one size and appear at regular or nearly regular intervals. Similarly, such skilled artisans will also recognize that decap cells can, and frequently are, sized to fit within and placed within the standard cell rows.)

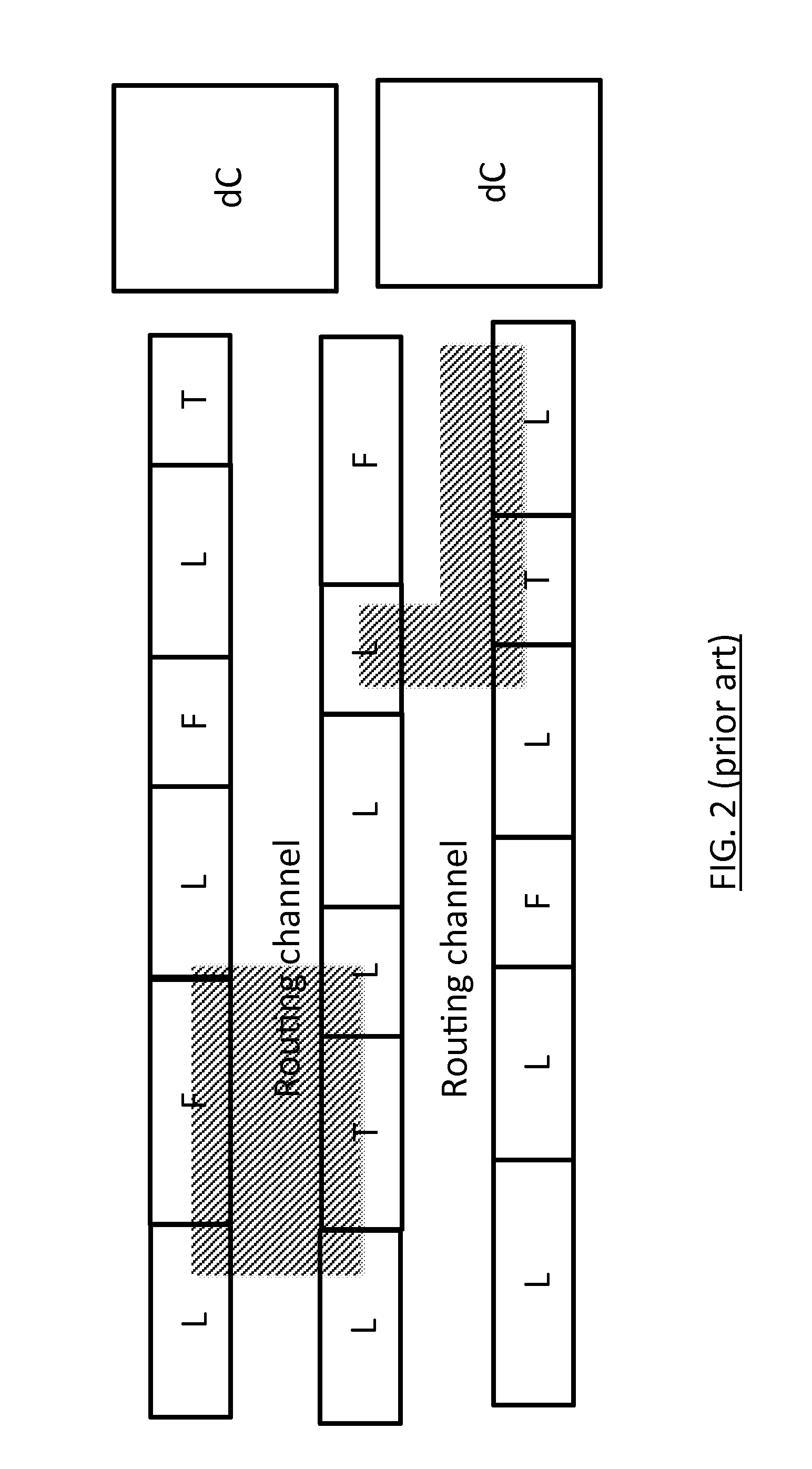

[0137]FIG. 2 conceptually depicts the same prior-art layout as FIG. 1, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More