Devices and methods of forming VFET with self-aligned replacement metal gates aligned to top spacer post top source drain EPI

a technology of metal gate and top source, which is applied in the direction of semiconductor devices, electrical equipment, transistors, etc., can solve the problems of limiting the thermal budget of the resultant device, complex realization of vfets with replacement metal gate (rmg) structures, and increasing the complexity of these structures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

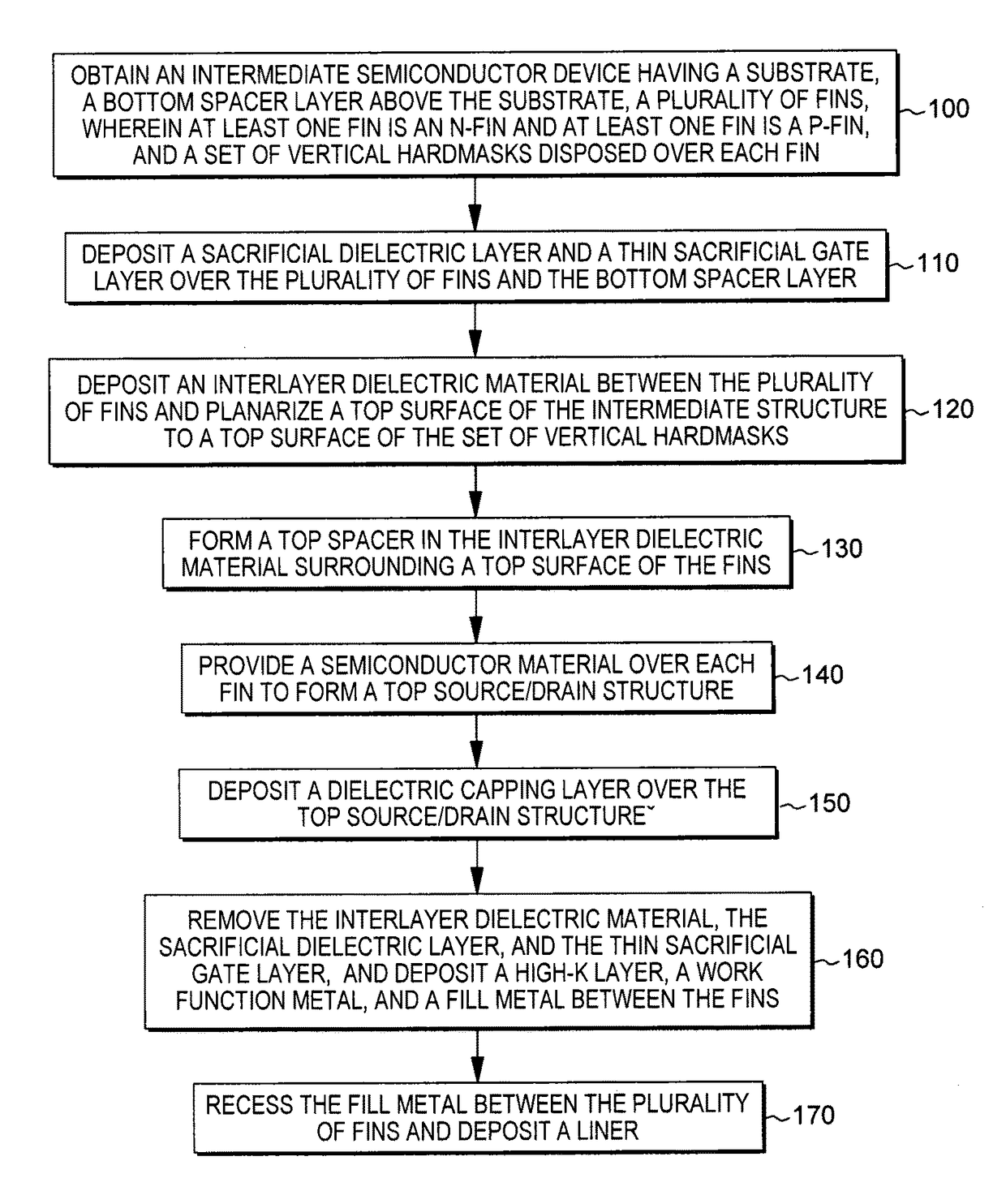

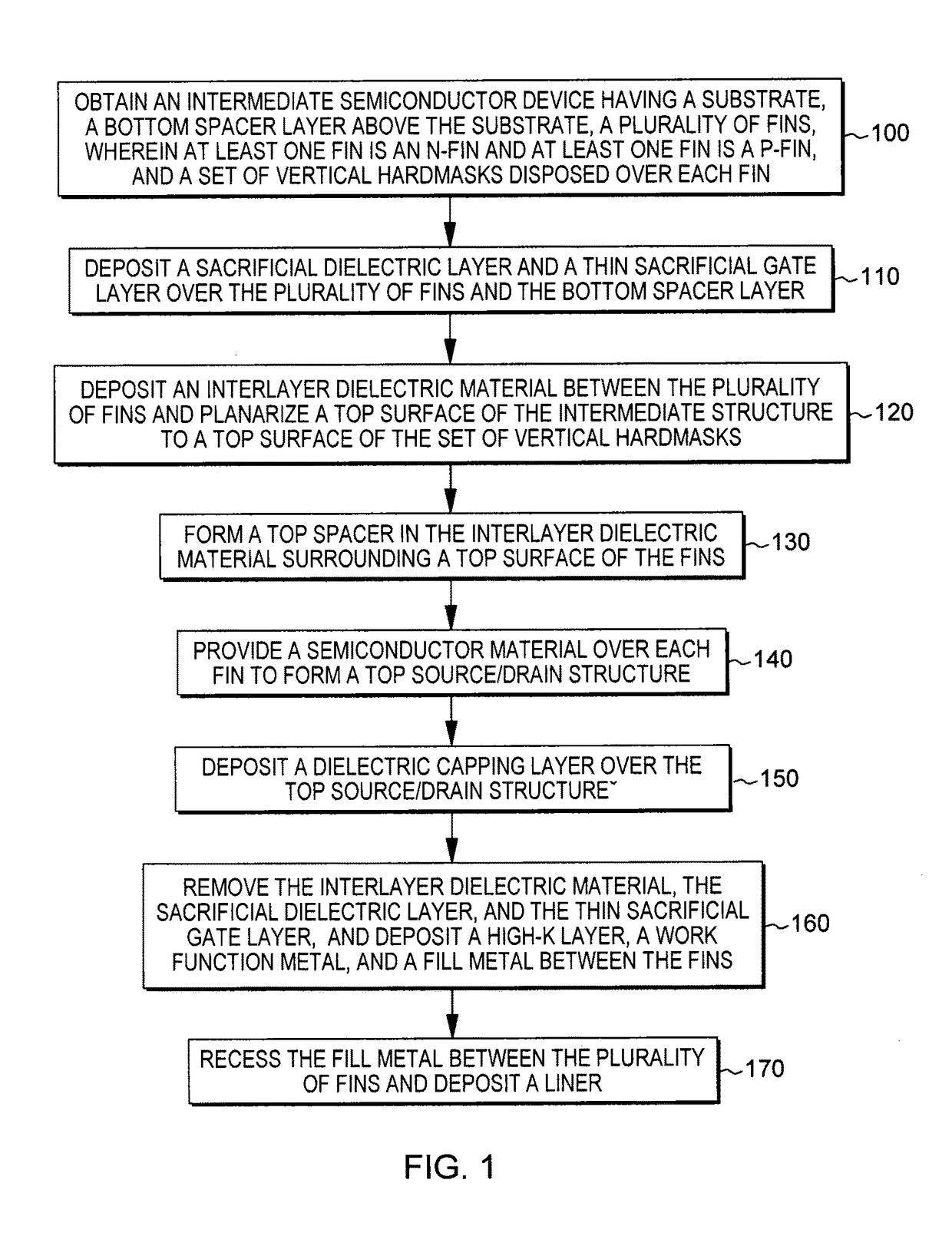

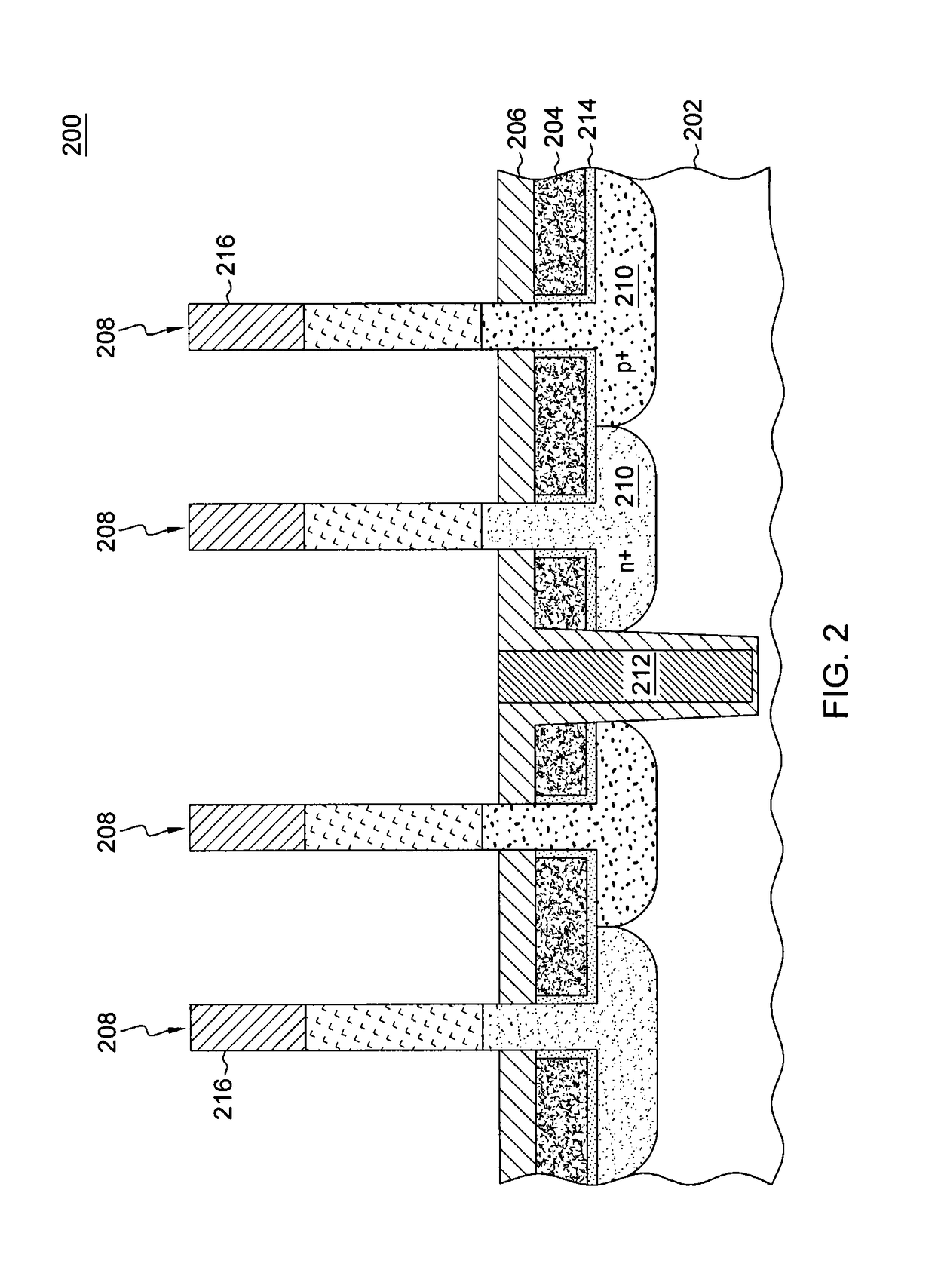

[0020]Aspects of the present invention and certain features, advantages, and details thereof, are explained more fully below with reference to the non-limiting embodiments illustrated in the accompanying drawings. Descriptions of well-known materials, fabrication tools, processing techniques, etc., are omitted so as to not unnecessarily obscure the invention in detail. It should be understood, however, that the detailed description and the specific examples, while indicating embodiments of the invention, are given by way of illustration only, and are not by way of limitation. Various substitutions, modifications, additions and / or arrangements within the spirit and / or scope of the underlying inventive concepts will be apparent to those skilled in the art from this disclosure. Note also that reference is made below to the drawings, which are not drawn to scale for ease of understanding, wherein the same reference numbers used throughout different figures designate the same or similar ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More