A device and method to eliminate signal burr

A technology for eliminating signals and burrs, which is applied in the field of signal processing, can solve problems such as narrow adaptation surface, and achieve the effect of wide adaptation range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will be further described in detail below in conjunction with the drawings and specific embodiments.

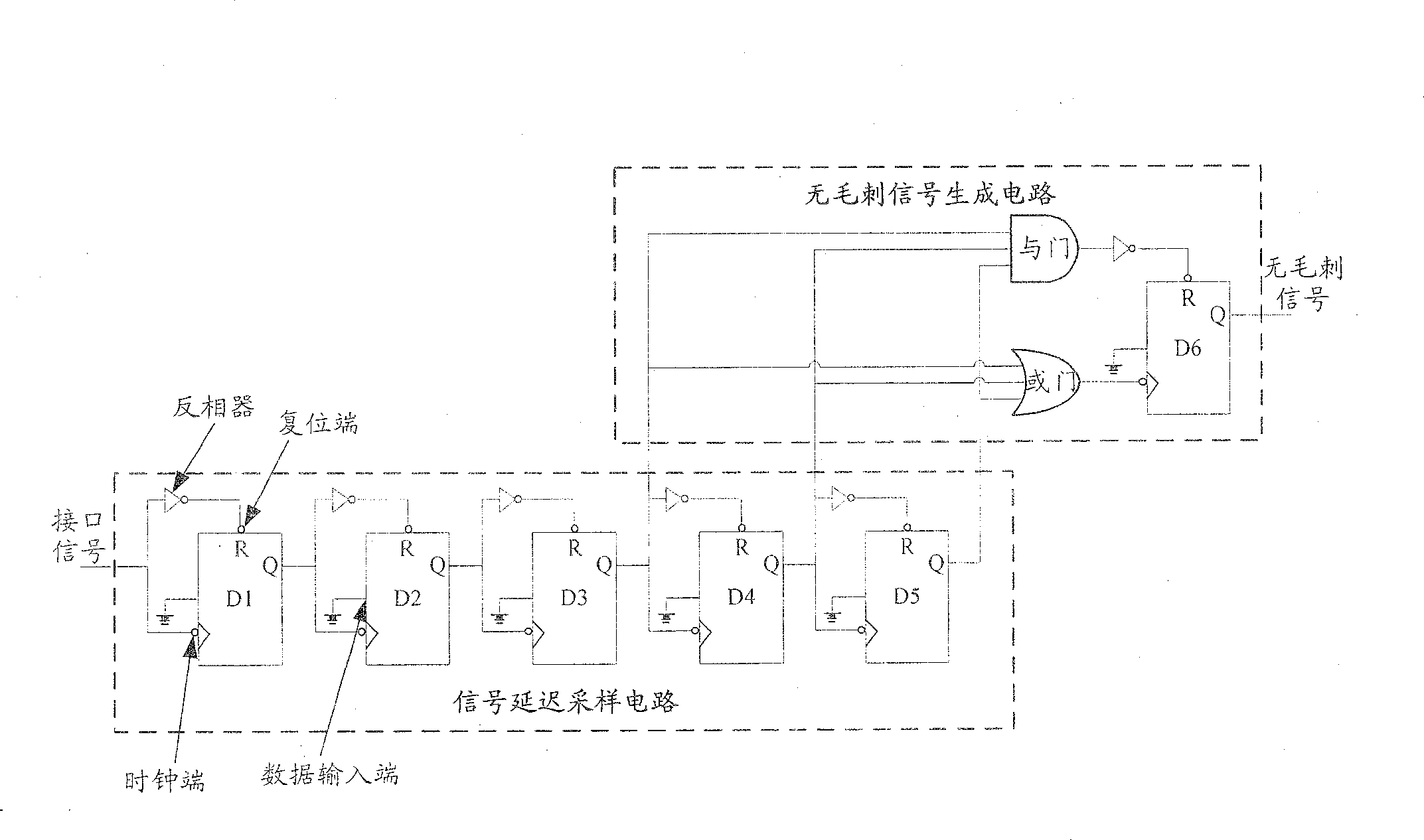

[0046] image 3 This is a diagram of an apparatus for eliminating glitches in a signal provided by an embodiment of the present invention, such as image 3 As shown, it mainly includes: signal delay sampling circuit and glitch-free signal generation circuit, among which:

[0047] Signal delay sampling circuit: used to perform N+m-level delay processing on the input interface signal to be removed from the burr. The delay time of the two adjacent stages is equal to Tclk-q, which will be obtained by the m+1~N+m-th stage delay processing The m+1~m+N-th stage delayed signal is output to the glitch-free signal generating circuit.

[0048] Here, Tclk-q is the length of time between the rising or falling edge of the clock end of the latch when the valid edge occurs to the time when the output of the latch changes; N is the maximum width of the glitch to be e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com