Sampling circuit and voltage sampling method for three-level power factor calibration circuit

A power factor correction, sampling circuit technology, applied in the direction of measuring electric power, electric power measurement through current/voltage, electric devices, etc., can solve problems such as negative interference of control circuit, eliminate negative interference, ensure normal bus voltage detection and safety. The effect of capacitance voltage difference detection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

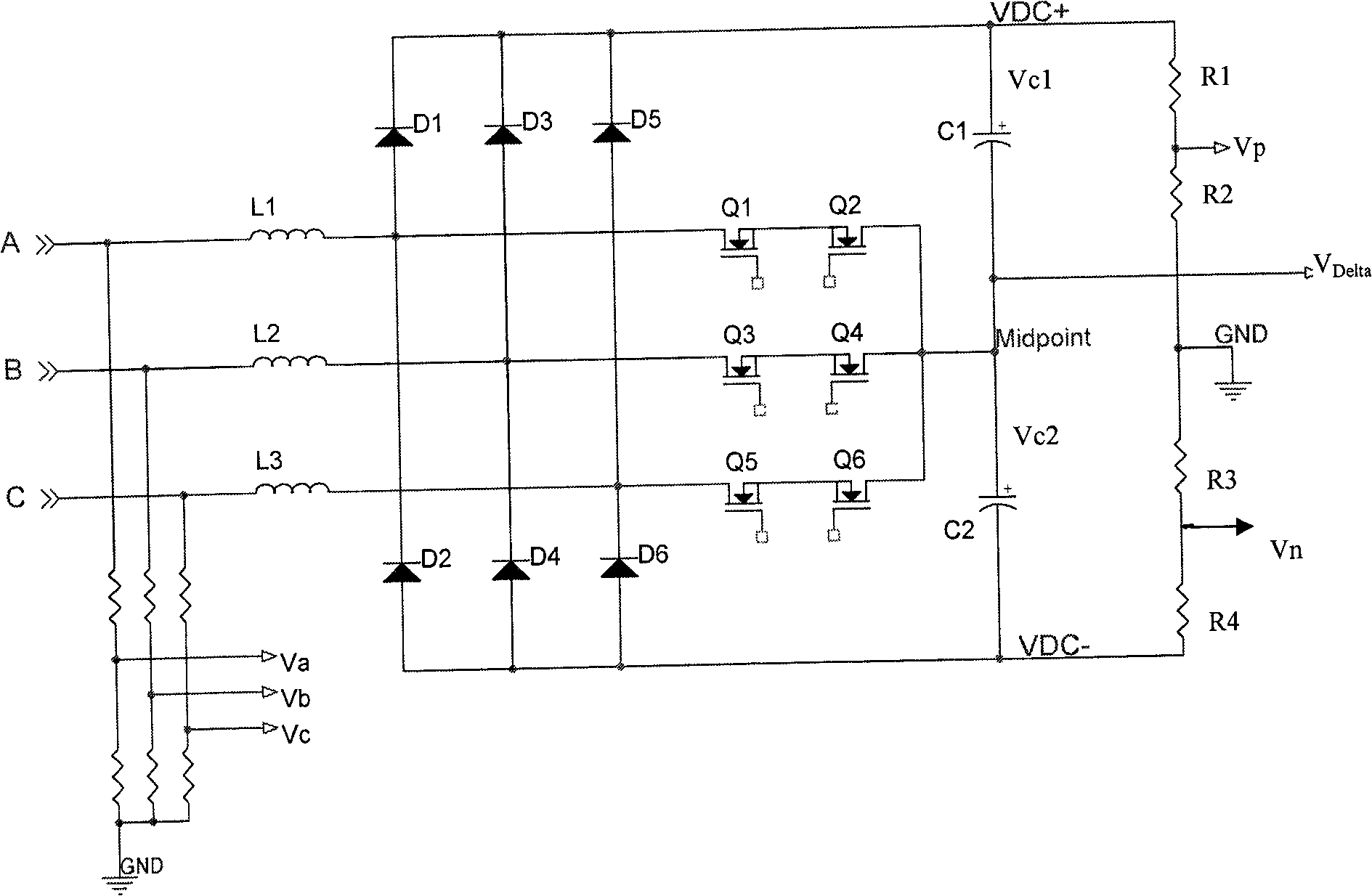

[0022] In a preferred embodiment of the present invention, according to image 3 The shown method samples the voltage of the three-level PFC circuit. from image 3 It can be seen from the figure 2 The difference is that: the midpoint (Midpoint) of the bus capacitors C1 and C2 is separated from the ground (GND) of the control circuit and is not connected together; the rest are the same.

[0023] exist image 3 In , the AC voltage sampling is also connected to the ground (GND) through the voltage divider resistors. Since the resistance values of these voltage divider resistors are very large, the ground (GND) is actually suspended; at this time, the capacitor at the midpoint High-frequency disturbance noise will no longer enter the control circuit in series. Although there are high-frequency disturbance noises at the busbars VDC+ and VDC-, because the resistance values of the voltage dividing resistors connecting them to the ground (GND) are very large, the high-frequen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More