TTL and CMOS compatible input buffer

An input buffer and input buffer technology, applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc. The effect of high consumption and high speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

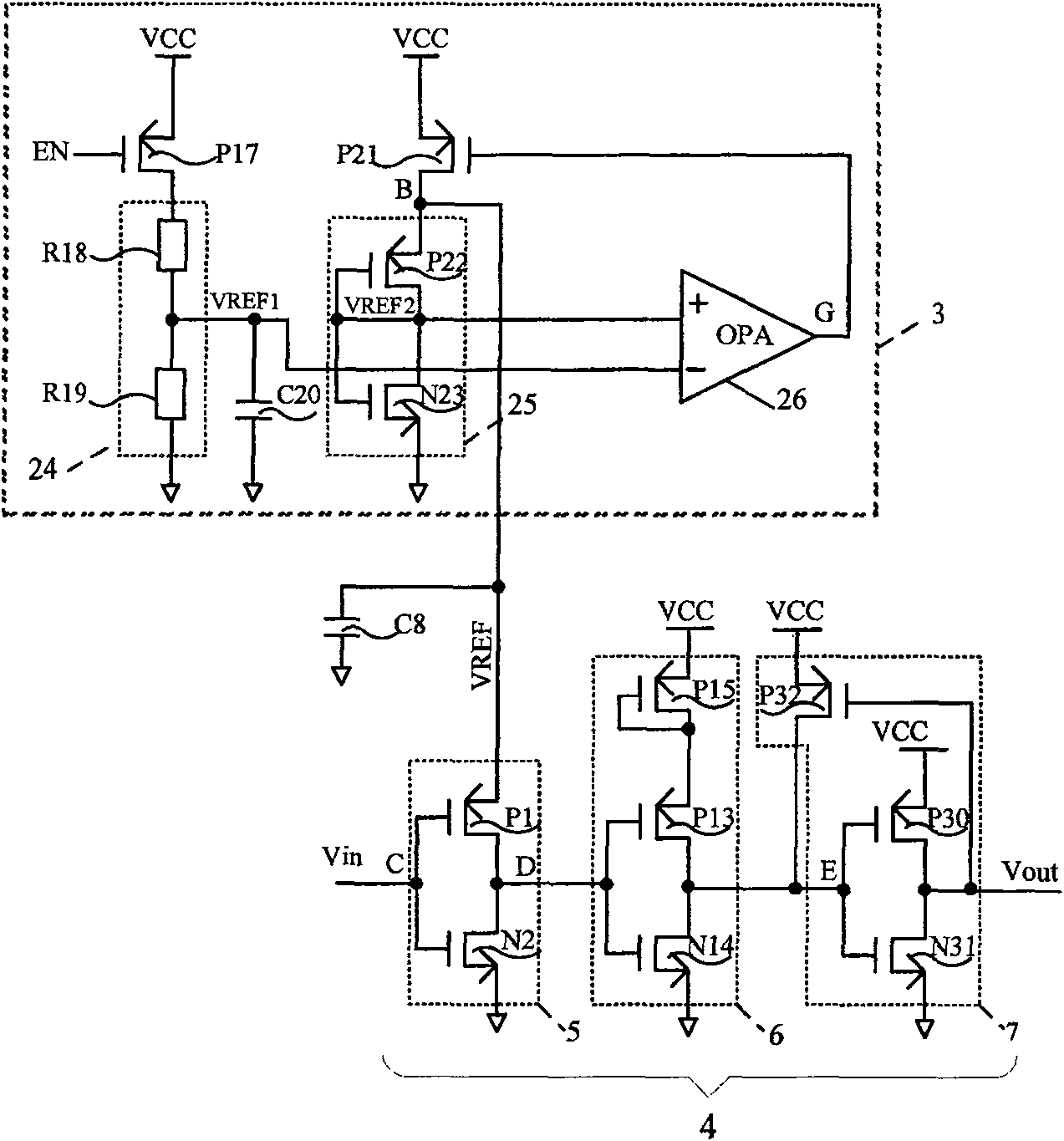

[0020] Such as figure 1 Shown is the schematic block diagram of the circuit of the TTL and CMOS compatible input buffer of the present invention, including a reference voltage generator 3 and an input buffer 4, and the reference voltage generator 3 includes a resistor divider network 24, a reference input buffer 25 and an operation The amplifier 26 and the input buffer 4 include an input inverter 5 , a second-stage input inverter 6 and a third-stage input inverter 7 .

[0021] The MOS transistors used in the present invention are all enhanced devices.

[0022] The input inverter 5 in the input buffer 4 is composed of a PMOS transistor P1 and an NMOS transistor N2, and the gate of the PMOS transistor P1 is connected to the gate of the NMOS transistor N2 as the input terminal of the input inverter 5, and the gate of the PMOS transistor P1 The drain is connected to the drain of the NMOS transistor N2 as the output of the input inverter 5 , the source of the NMOS transistor N2 is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More