Memory device detecting method

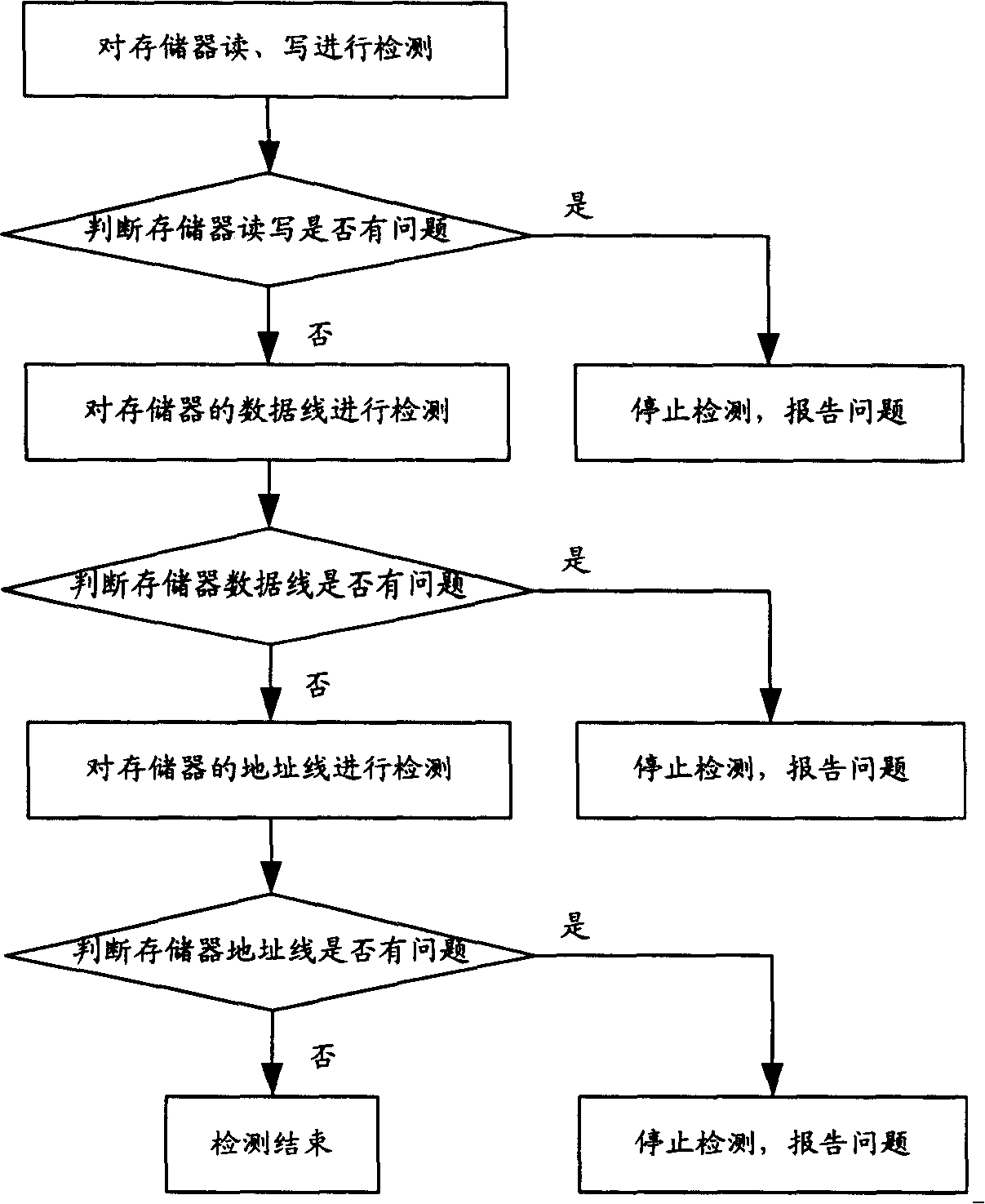

A detection method and memory technology, applied in static memory, instruments, etc., can solve problems such as virtual welding, adhesion, and complex address line detection process, and achieve the effect of improving detection efficiency and accurate detection results.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

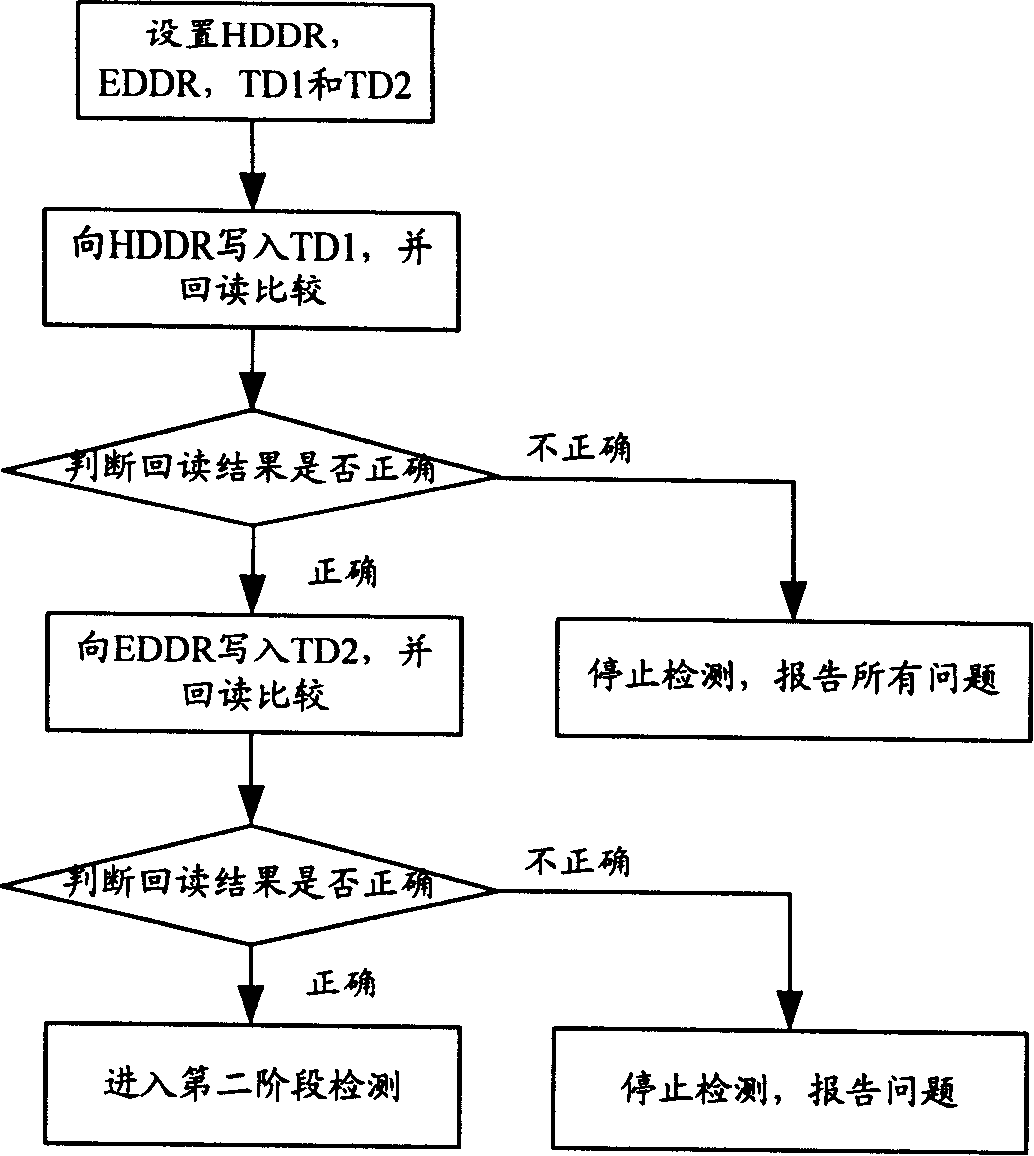

[0076] The first stage, reading and writing detection:

[0077] 1. HDDR is 0X0000000, because the odd address of the memory cannot be read and written, so EDDR is 0X1FFFFFE; for the convenience of detection and calculation, set TD1 to "all 0", that is, 0X0000, and TD2 to "all 1", that is, 0XFFFF,

[0078] TD1 and TD2 are interchangeable, which does not affect the implementation of the present invention. The reason why TD1 and TD2 are set to "all 0" and "all 1" is to facilitate the setting of TDG1 and TDG2 in the subsequent second and third stages;

[0079] 2. Write TD1 into HDDR, read back and compare, if the result is correct, it means that each data line is set to a low level '0' and it can be normal, which can eliminate the problem that the data line is always a high level '1', and then , go to the next step; if the result is incorrect, it means that there is a problem with HDDR or address line or data line reading and writing, stop testing and report the problem;

[0080]...

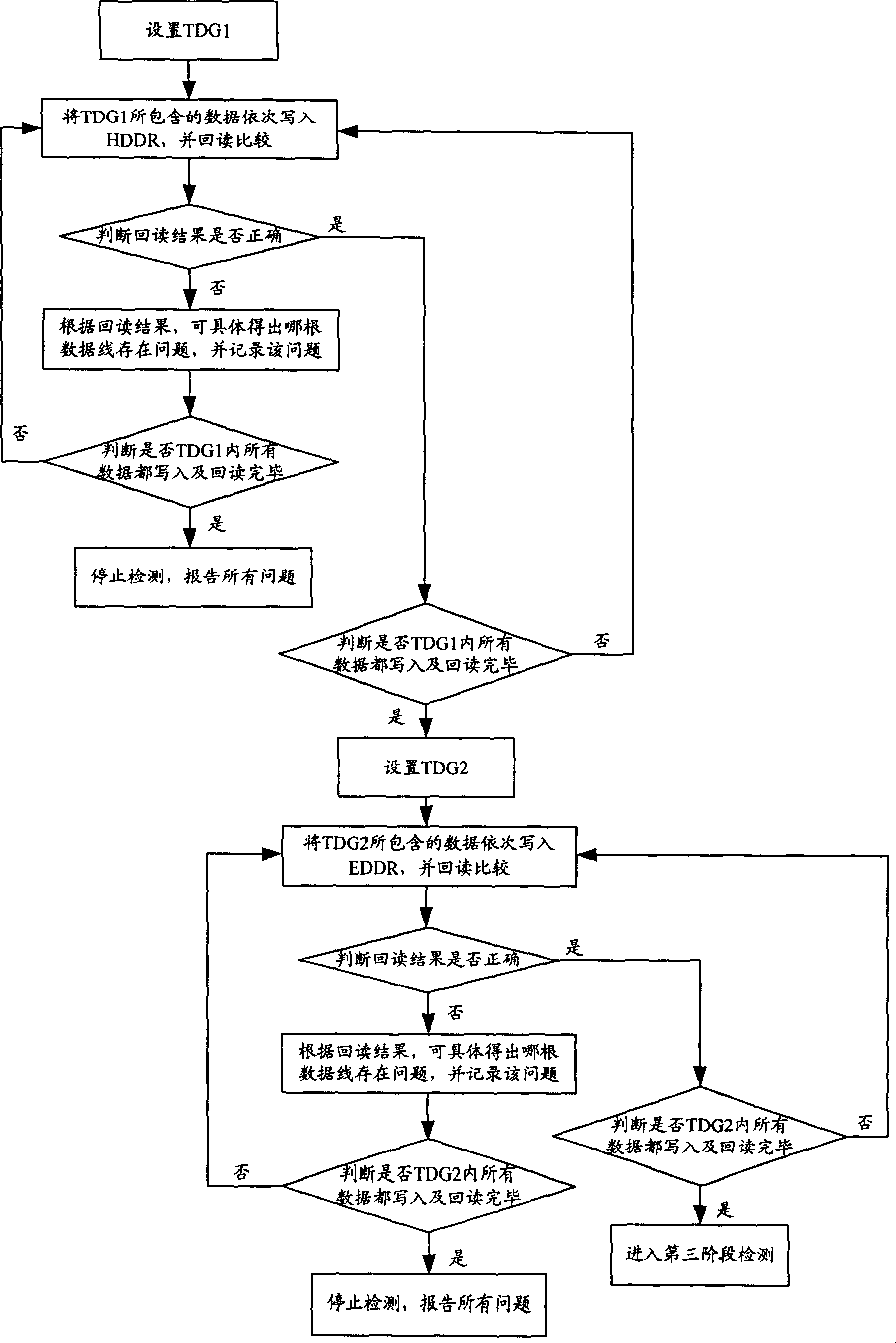

Embodiment 2

[0132] The difference between this embodiment and embodiment 1 is: in the second stage and the third stage of embodiment 1, if a certain data line or address line is found to have a fault, then record the fault, and then continue to detect, and in the In this embodiment, in the second and third stages, as soon as a fault is found in the data line or address line, the detection is stopped and the problem is reported. After the fault is eliminated, the detection of the memory is restarted. The detection process of the second stage and the third stage of the present embodiment are respectively as follows Figure 5 and Figure 6 shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More