Scheduling method of silicon slice transmission course

A technology of transmission process and scheduling method, applied in the direction of conveyor objects, transportation and packaging, electrical program control, etc., can solve the problems of long manufacturing cycle and low production efficiency, and achieve short manufacturing cycle, high production efficiency, and silicon wafer transmission reasonable effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

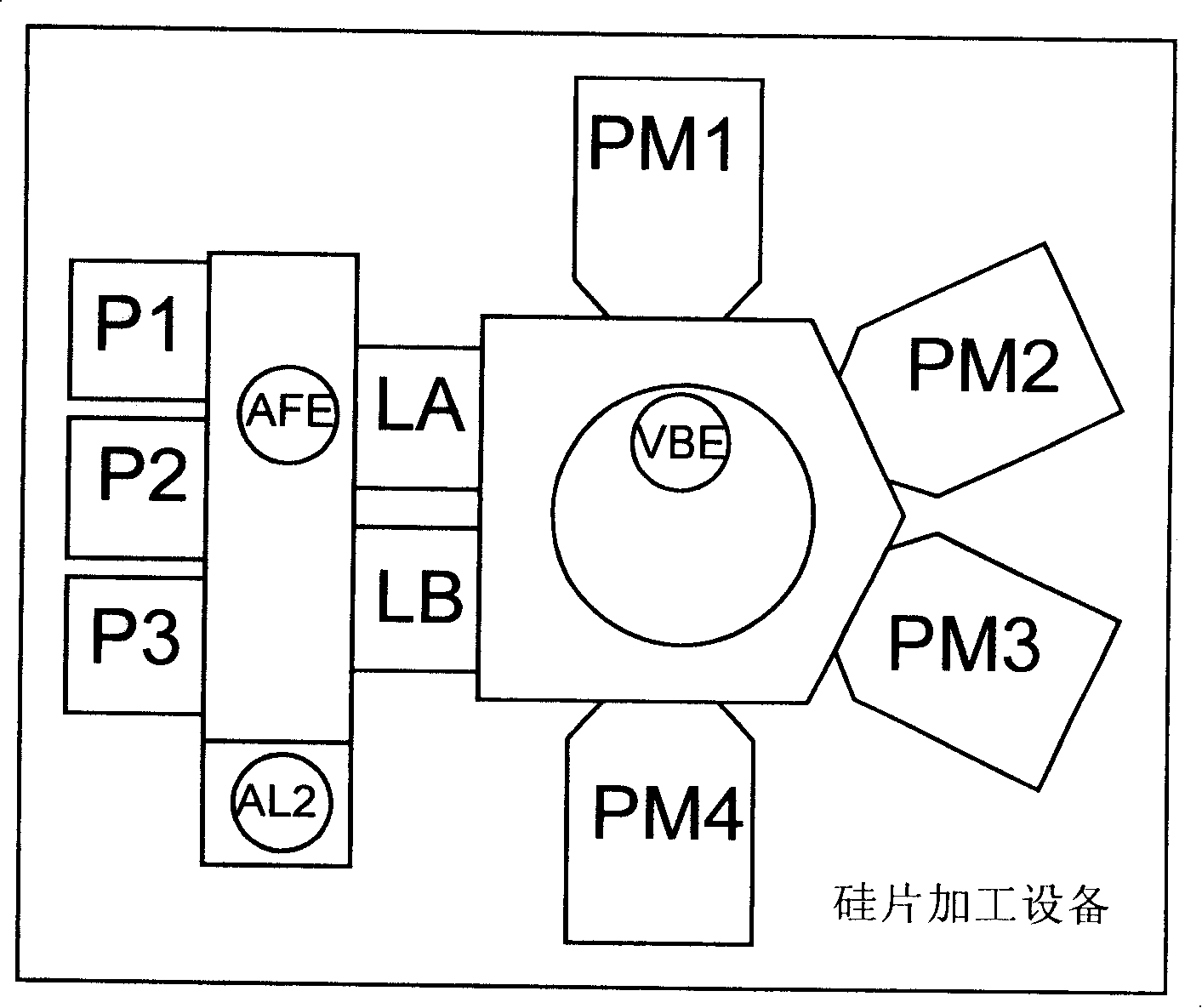

[0034] The scheduling method of the silicon chip transmission process of the present invention is mainly used in the semiconductor silicon chip processing process to schedule the transmission paths of a plurality of silicon chips in N nodes in the silicon chip processing equipment, wherein N is a positive integer, and can also be used For the scheduling of other transmission equipment.

[0035] Such as figure 1 As shown, the silicon wafer processing equipment includes the following nodes:

[0036] The first film chamber P1; the second film chamber P2; the third film chamber P3; the positioning calibration device AL2; the first vacuum lock LA; the second vacuum lock LB; the atmospheric manipulator AFE; the vacuum manipulator VBE; the first reaction chamber PM1; The second reaction chamber PM2; the third reaction chamber PM3; the fourth reaction chamber PM4.

[0037] The scheduling method of the silicon chip transmission process of the present invention can calculate the short...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More