Space vector width pulse modulation method based on FPGA

A technology of space vector pulse width and modulation method, applied in vector control systems, control systems, control generators, etc., can solve the problems of complex calculation and difficult implementation, and achieve the effect of flexible programming

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

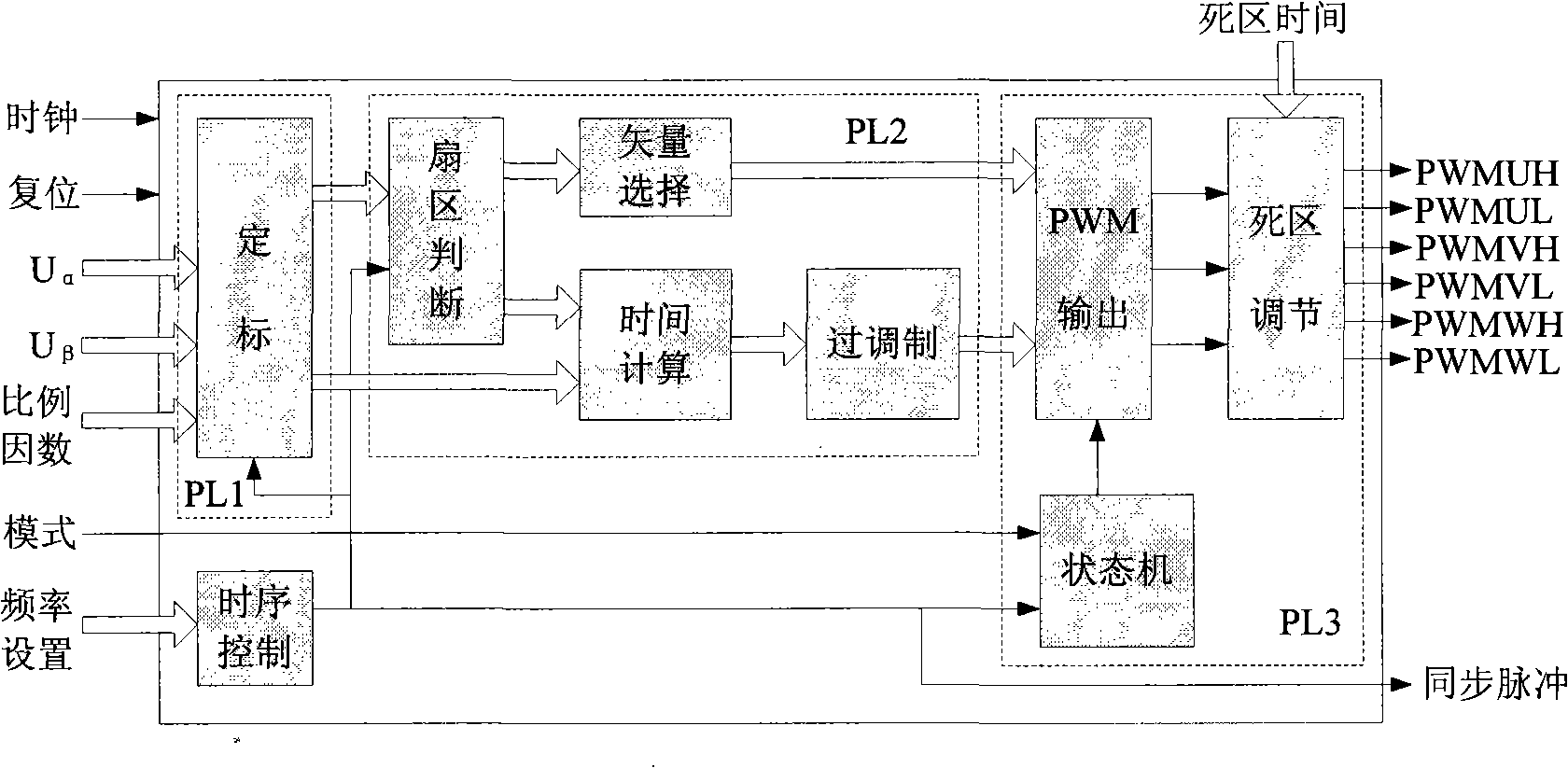

[0023] A kind of method that the present invention proposes realizes Space Vector Pulse Width Modulation (SVPWM) algorithm on FPGA, this method utilizes the design idea of FPGA modularization to divide SVPWM algorithm into such as figure 1 For the nine modules shown, the specific implementation method of each module will be introduced in detail below.

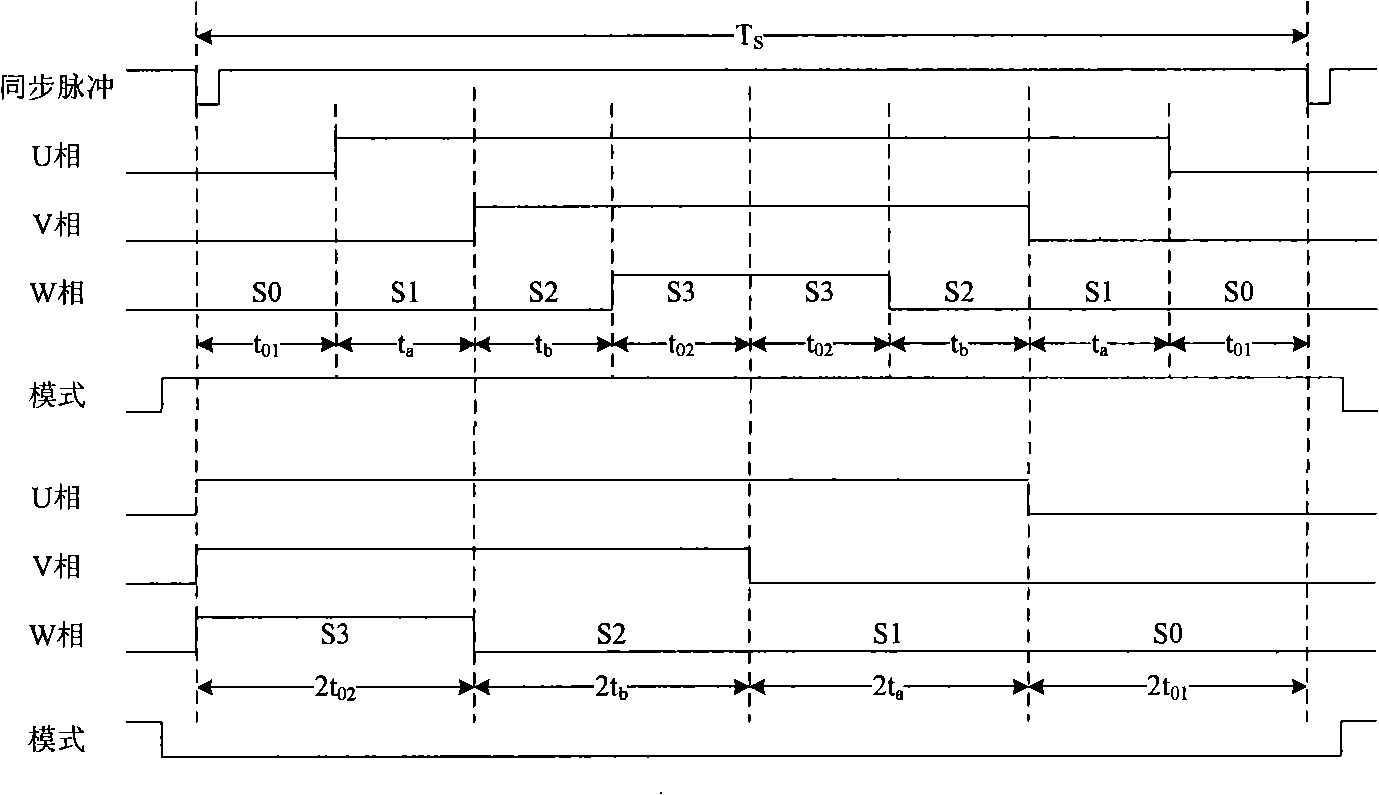

[0024] Step one, timing control. The timing control module adopts the synchronous pulse generated by the adjustable up-down counter, and the synchronous pulse acts on the figure 1 Three blocks of PL1, PL2 and PL3, including all other modules in the scheme. By detecting the falling edge of the synchronization pulse to trigger the circuit to ensure the synchronization of each module, the three circuits of PL1, PL2 and PL3 constitute a three-stage pipeline. The period Ts of the synchronous pulse is the period of the PWM wave, and considering that SVPWM is only a functional module in a complete AC servo system, the synchronous ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More