Clock switch circuit

A clock switching and circuit technology, applied in the direction of electrical components, pulse processing, signal generation/distribution, etc., can solve problems such as glitches, application circuit errors, wrong actions, etc., and achieve the effect of avoiding glitches and metastable states

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

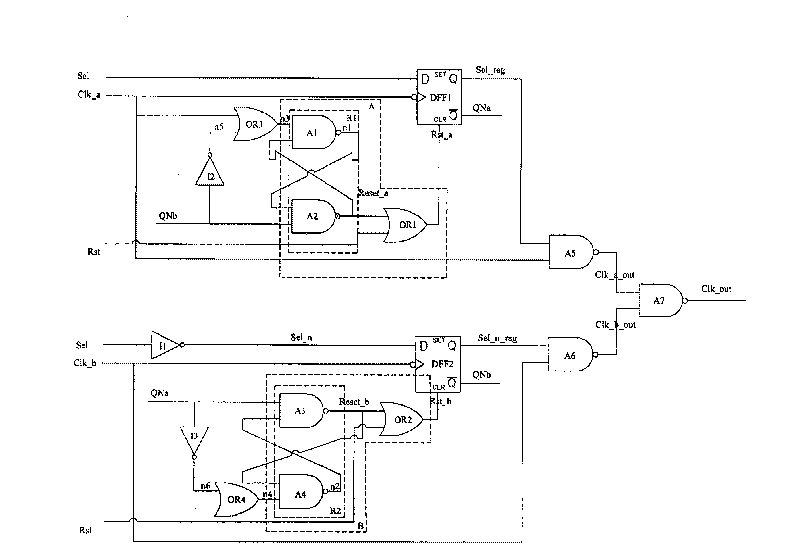

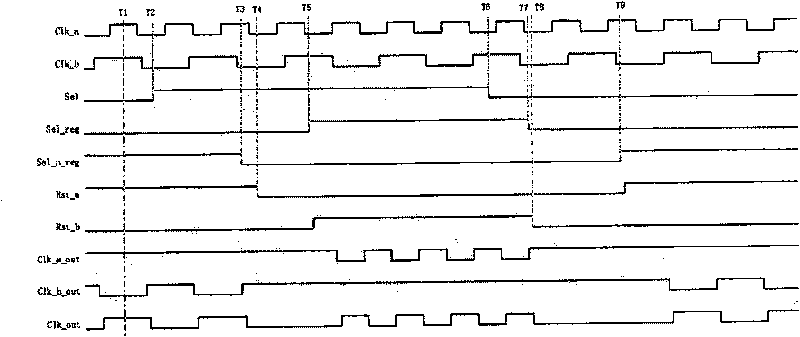

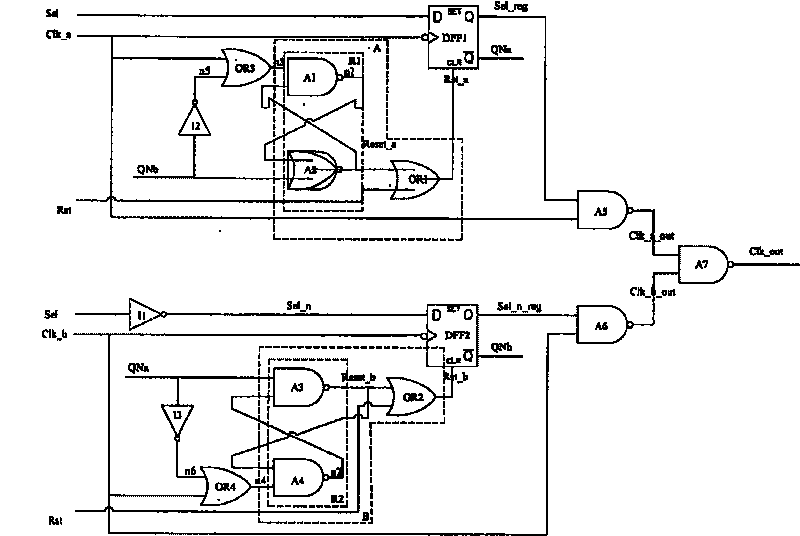

[0014] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments. The clock switching circuit of the present invention adopts an asynchronous reset method to synchronize the clock selection signal and the clock signal, switches between the irrelevant first clock signal Clk_a and the second clock signal Clk_b according to the selection signal Sel, and outputs a glitch-free clock Output signal Clk_out, and avoid metastability problem.

[0015] The clock switching circuit of the present invention is composed of two reset generating circuits, two OR gates, three NOT gates, two D flip-flops and a clock output circuit. Such as figure 1 As shown, the first reset generating circuit A and the second reset generating circuit B are respectively connected to the first D flip-flop DFF1 and the second D flip-flop DFF2, the two D flip-flops are triggered by the falling edge of the clock and have an asynchronous reset termin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More