Method for SOC (system on chip) asynchronous clock domain signal interface

A signal interface and asynchronous clock technology, applied in the field of VLSI and integrated circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0021] 1. Explanation of circuit connection, device function, and signal naming:

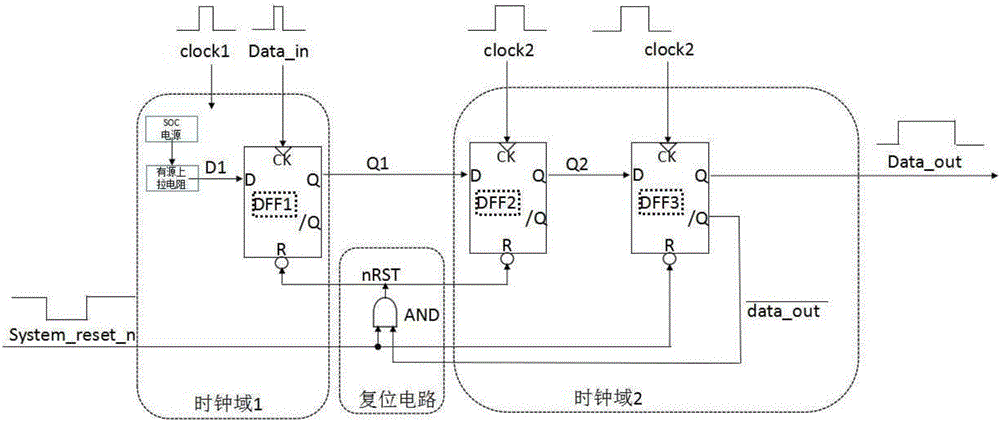

[0022] Such as figure 1 As shown, the circuit uses 4 devices, three latches and one gate unit.

[0023] They are respectively: the first latch DFF1, the second latch DFF2, the third latch DFF3, and the gate unit AND. The type of latch is: synchronous flip-flop with asynchronous reset terminal. The asynchronous reset terminal is defined as R, the synchronous clock terminal is defined as CK, the data input terminal is named D, the data output terminal is named Q, and the inverted data output terminal is named / Q. The input terminals include: D, R, CK; the output terminals include: Q, / Q. The function description is as follows: asynchronous reset terminal R, when input low level "0" (other input terminals can be any value), Q terminal output low, / Q ou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More