Multi-stage test response compactors

A compressor and tested technology, applied in the direction of electronic circuit testing, instrumentation, measuring electronics, etc., to achieve high diagnostic resolution and reduced test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 100

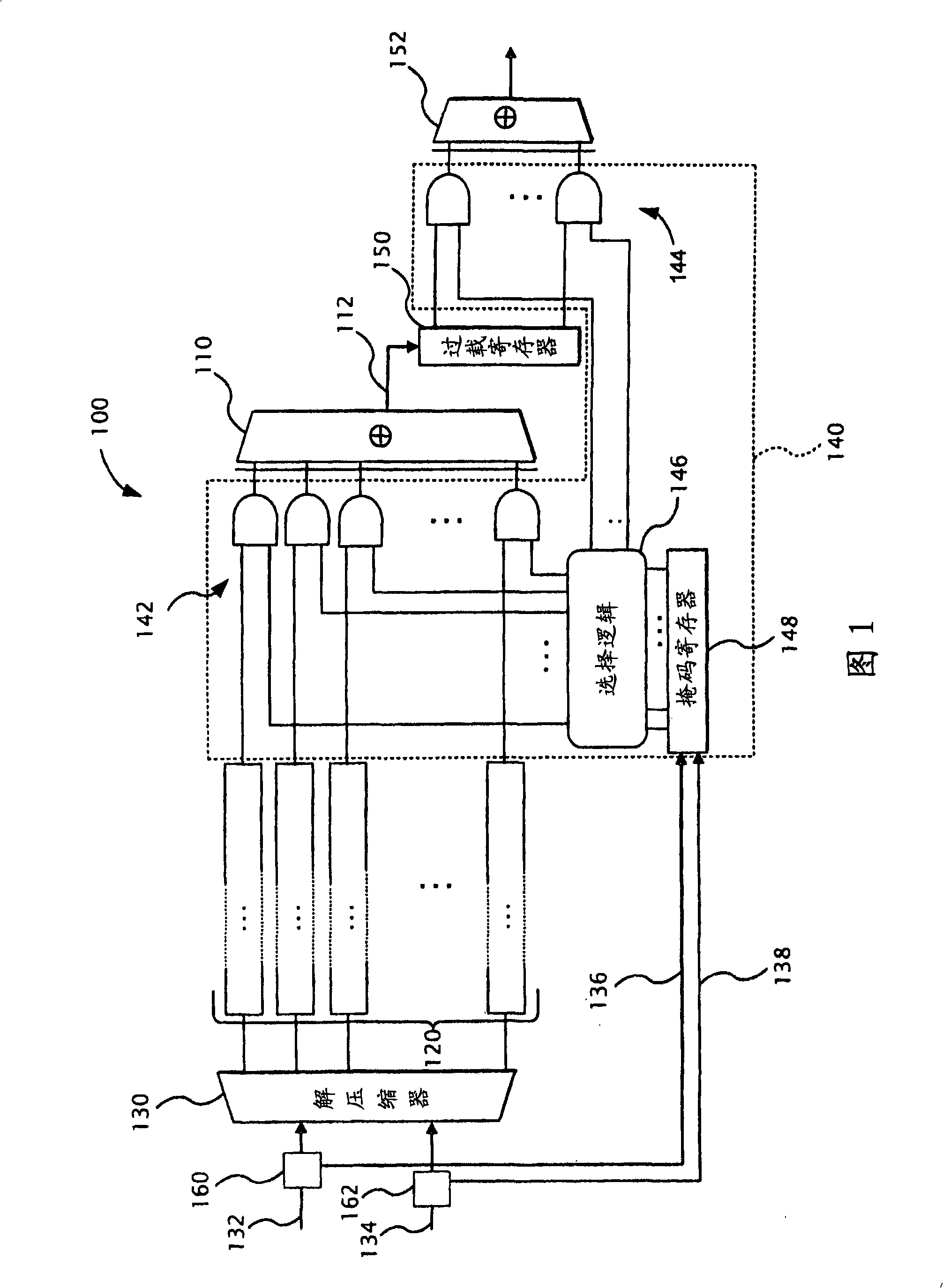

[0066] 1 shows an exemplary implementation 100 of a compressor architecture (X-Press compressor architecture) in an embedded deterministic test environment with n scan chains 120, which includes a first test response compressor 110 and a second test Response compressor 152 . A compressed test stimulus may be provided to scan chain 120 via decompressor 130 via one or more input channels (or input paths) 132 , 134 . In some embodiments, these channels may also be used in conjunction with input channels 136 , 138 to deliver mask bits (mask instructions) to selector circuit 140 via components 160 , 162 . In certain implementations, the components 160, 162 are pipeline registers, while in other implementations they may be demultiplexers. In other embodiments, there may not necessarily be a data dependency between the compressed test stimulus and the mask bits, as discussed more fully below. Compressor 110 may be a spatial compressor (or spatial compressor) including an XOR or XNO...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More