Method and system for regulating CPU clock frequency

A clock frequency and clock switching technology, applied in the field of communication, can solve the problems of increasing system logic complexity and increasing system efficiency, and achieve the effect of reducing system logic complexity and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

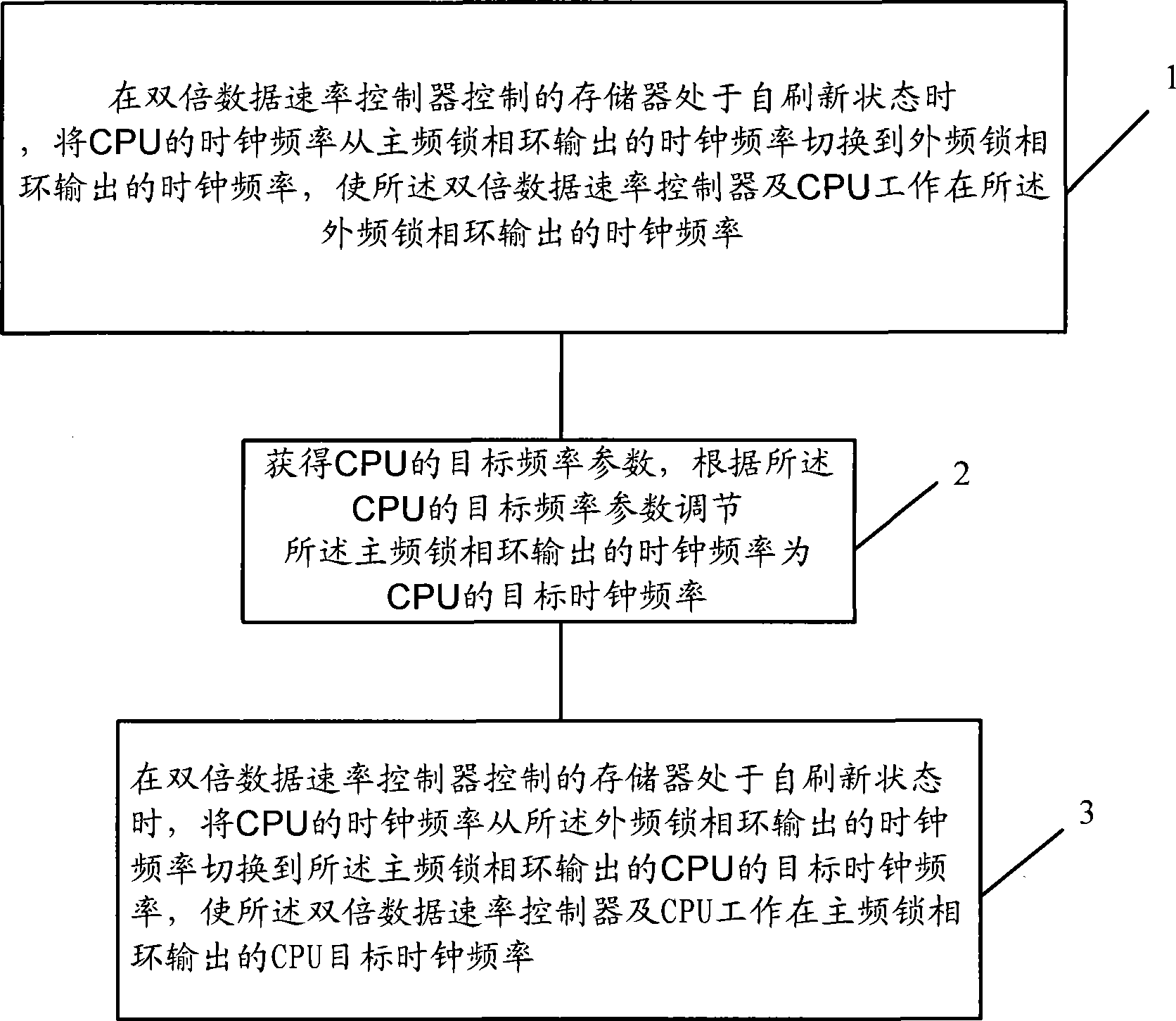

[0032] Such as image 3 As shown, a method for adjusting the CPU clock frequency includes:

[0033] Step 1: When the memory controlled by the double data rate controller is in the self-refresh state, switch the clock frequency of the CPU from the clock frequency output by the main frequency phase-locked loop to the clock frequency output by the external frequency phase-locked loop, so that the double data rate The rate controller and the CPU work at the clock frequency output by the external frequency phase-locked loop;

[0034] Step 2: Obtain the target frequency parameter of the CPU, and adjust the clock frequency output by the main frequency phase-locked loop to be the target clock frequency of the CPU according to the target frequency parameter of the CPU;

[0035] Step 3: When the memory controlled by the double data rate controller is in the self-refresh state, switch the clock frequency of the CPU from the clock frequency output by the external frequency phase-locked l...

Embodiment 2

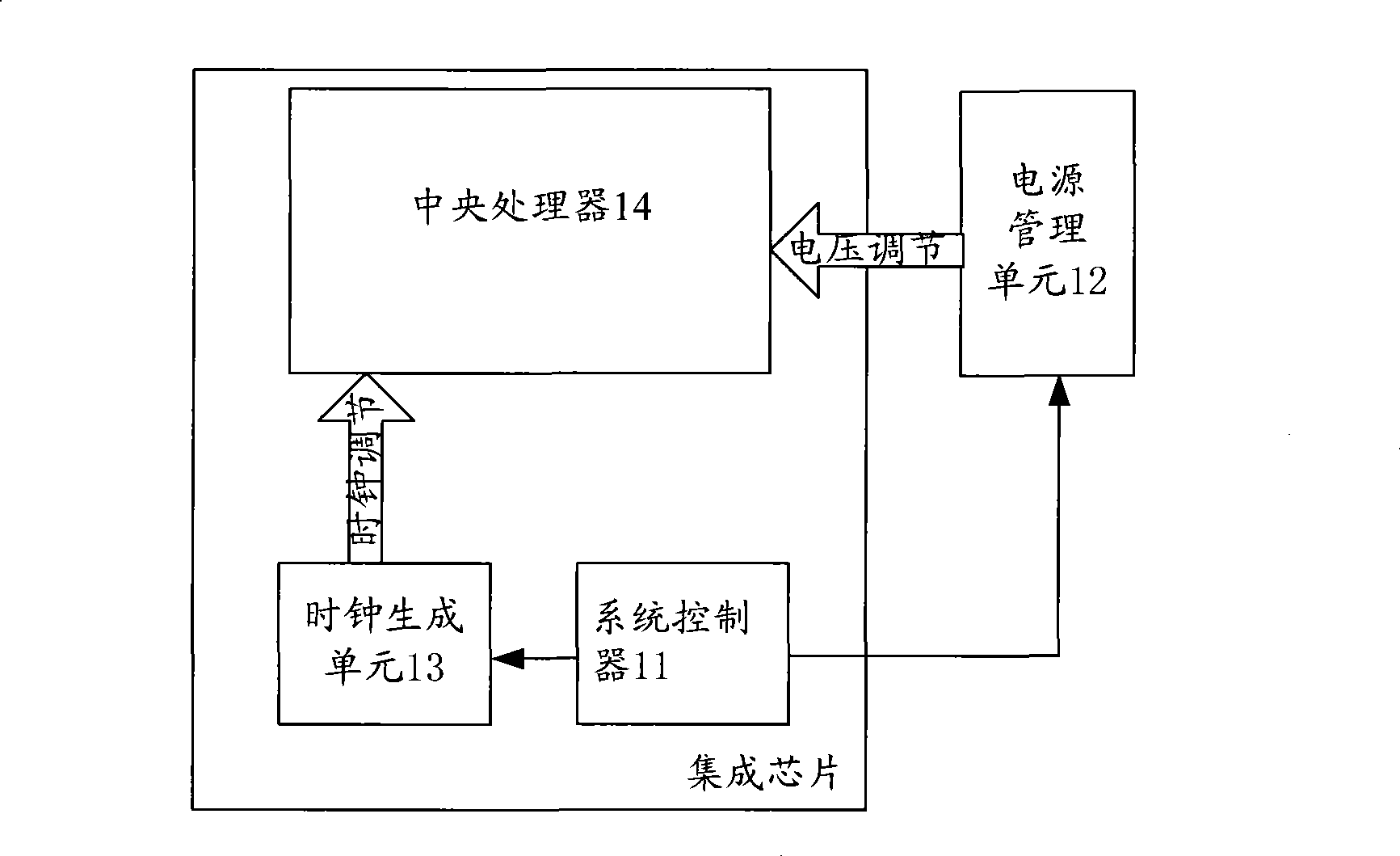

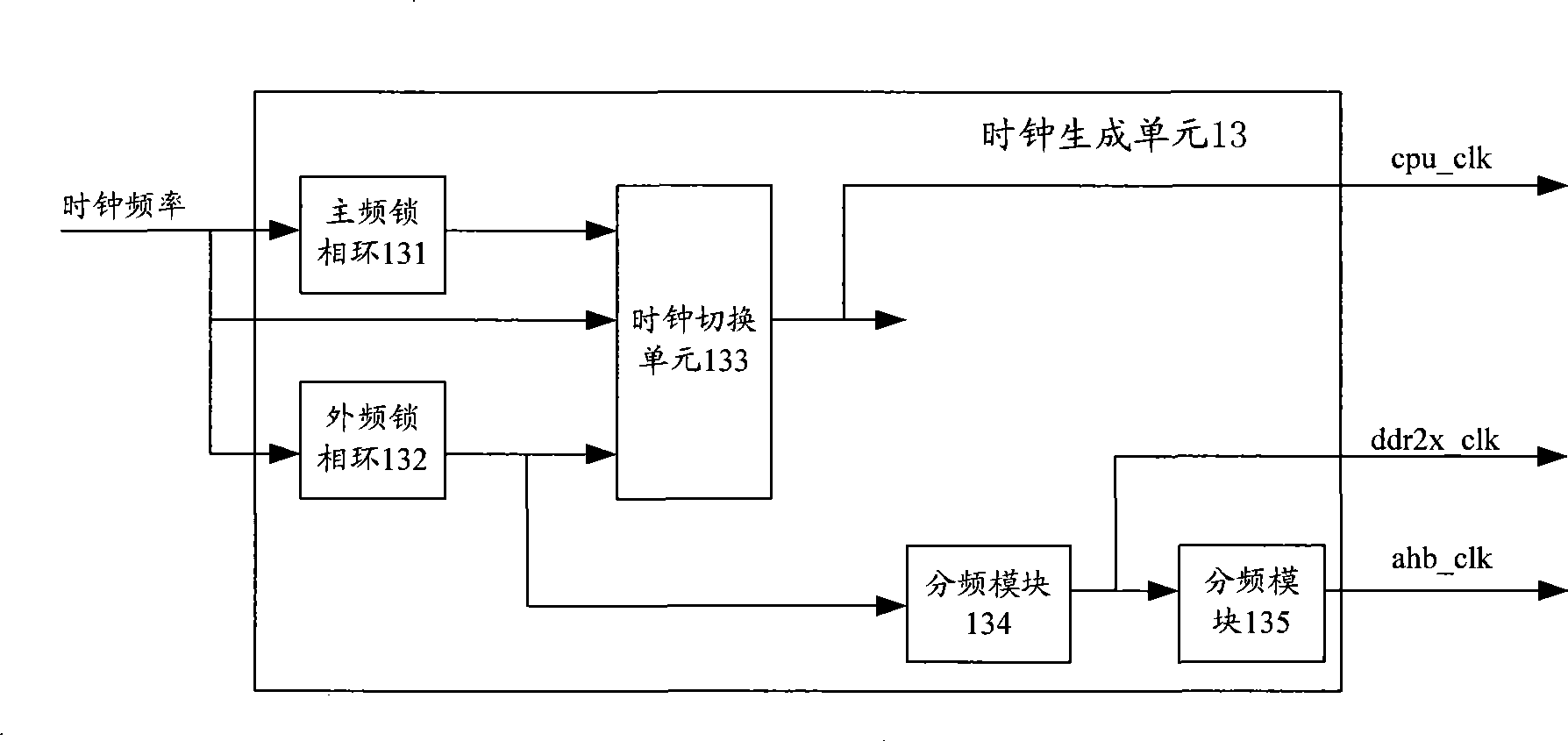

[0095] Such as Figure 6 and Figure 8 As shown, a system for adjusting the CPU clock frequency includes a system controller 5 and a clock generation unit 6, wherein the clock generation unit 6 includes a main frequency phase-locked loop 61, an external frequency phase-locked loop 62 and a clock switching unit 63,

[0096] The system controller 5 is used to determine that after the memory controlled by the double data rate controller is in the self-refresh state, control the clock switching unit 63 to switch the clock, and the clock switching unit 63 outputs the clock frequency of the CPU from the main frequency phase-locked loop 61 The clock frequency is switched to the clock frequency output by the external frequency phase-locked loop 62, so that the double data rate controller and the CPU work at the clock frequency output by the external frequency phase-locked loop 62;

[0097] The system controller obtains the target clock frequency parameter of the CPU, and adjusts the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More