Method for manufacturing hyperconjugation VDMOS device

A device and lithography technology, which is applied in the field of preparation of power metal oxide semiconductor field effect transistor devices to achieve the effects of reducing on-resistance and on-state power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

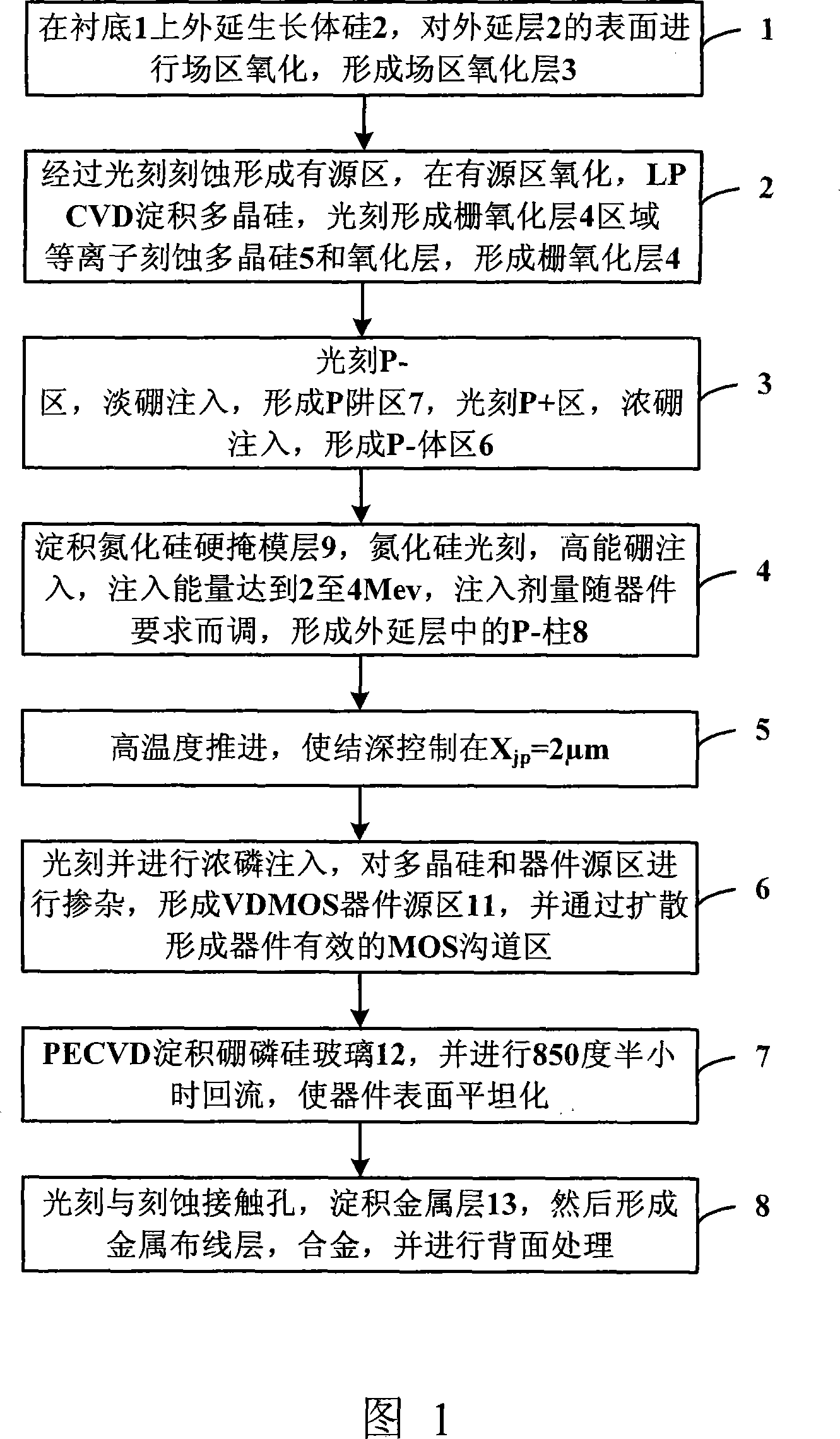

[0040] like figure 1 as shown, figure 1 It is a flow chart of a method for preparing a super junction VDMOS provided by the present invention, and the method includes the following steps:

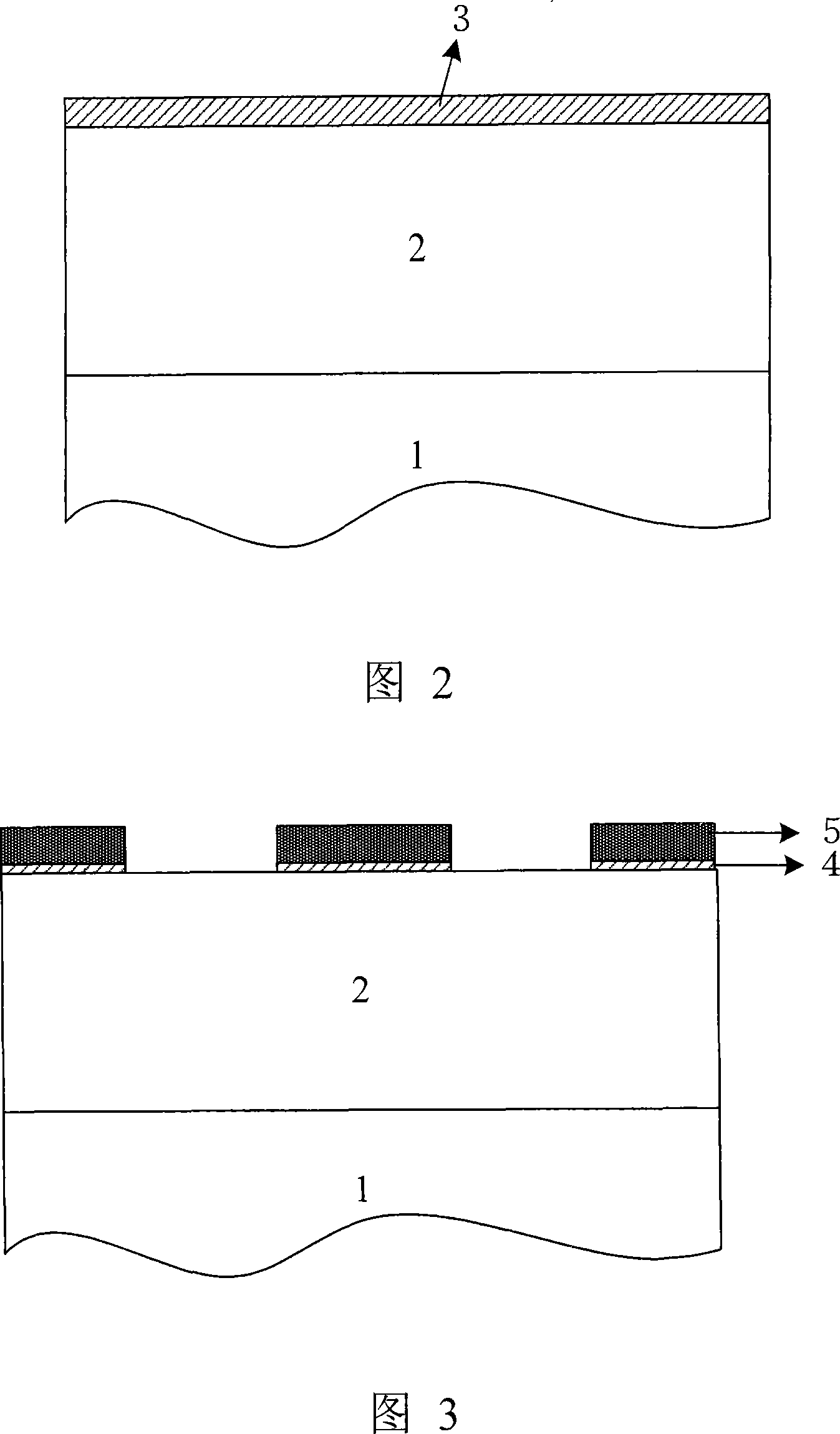

[0041] Step 1, epitaxially growing bulk silicon 2 on the substrate 1, performing field oxidation on the surface of the epitaxial layer 2, to form a field oxide layer 3;

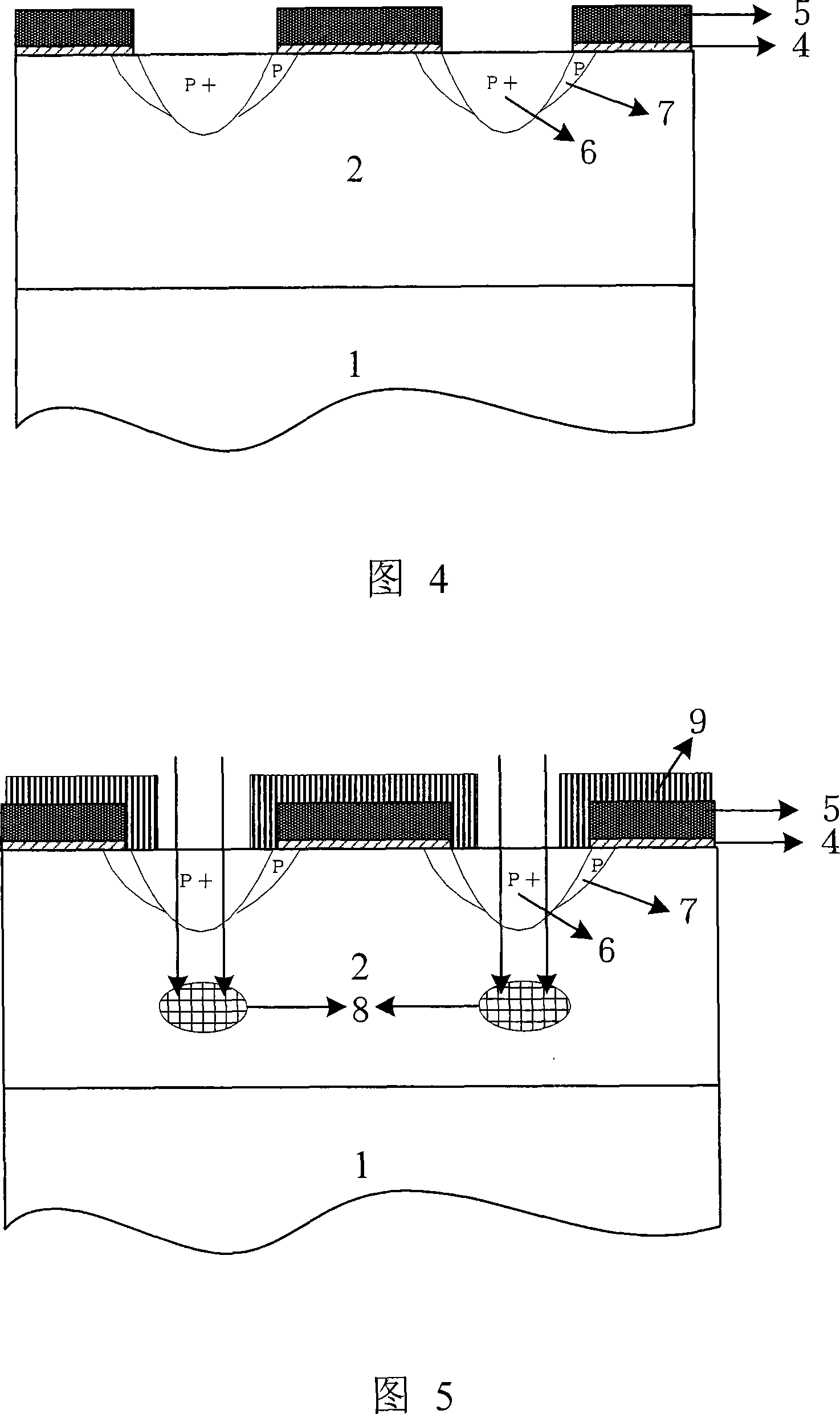

[0042] Step 2, forming an active area through photolithography, oxidation in the active area, LPCVD deposition of polysilicon, photolithography to form the area of the gate oxide layer 4, plasma etching of the polysilicon 5 and the oxide layer to form the gate oxide layer 4;

[0043] Step 3, photoetching the P-region, implanting light boron to form the P well re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More