MOS component testing method

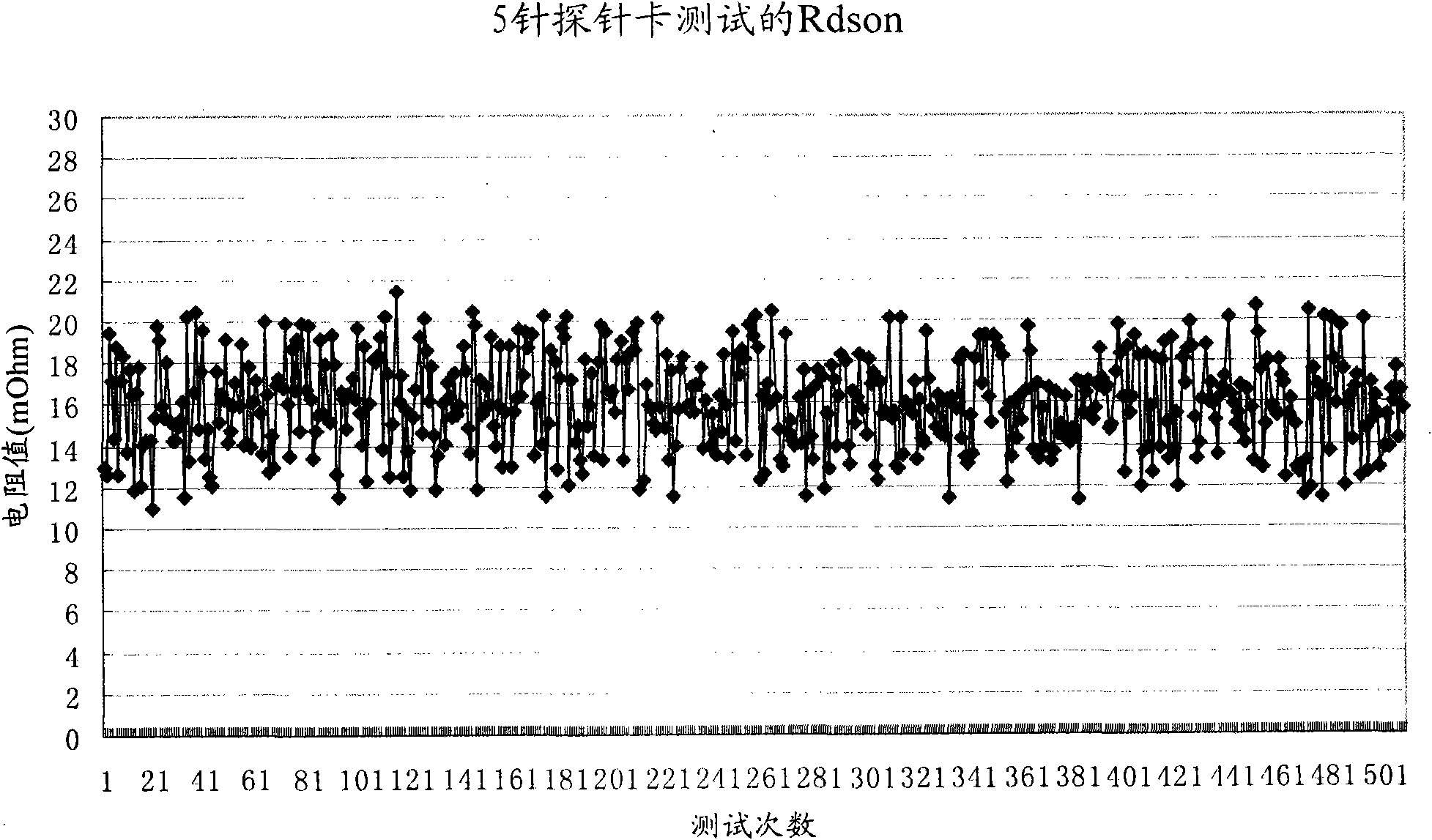

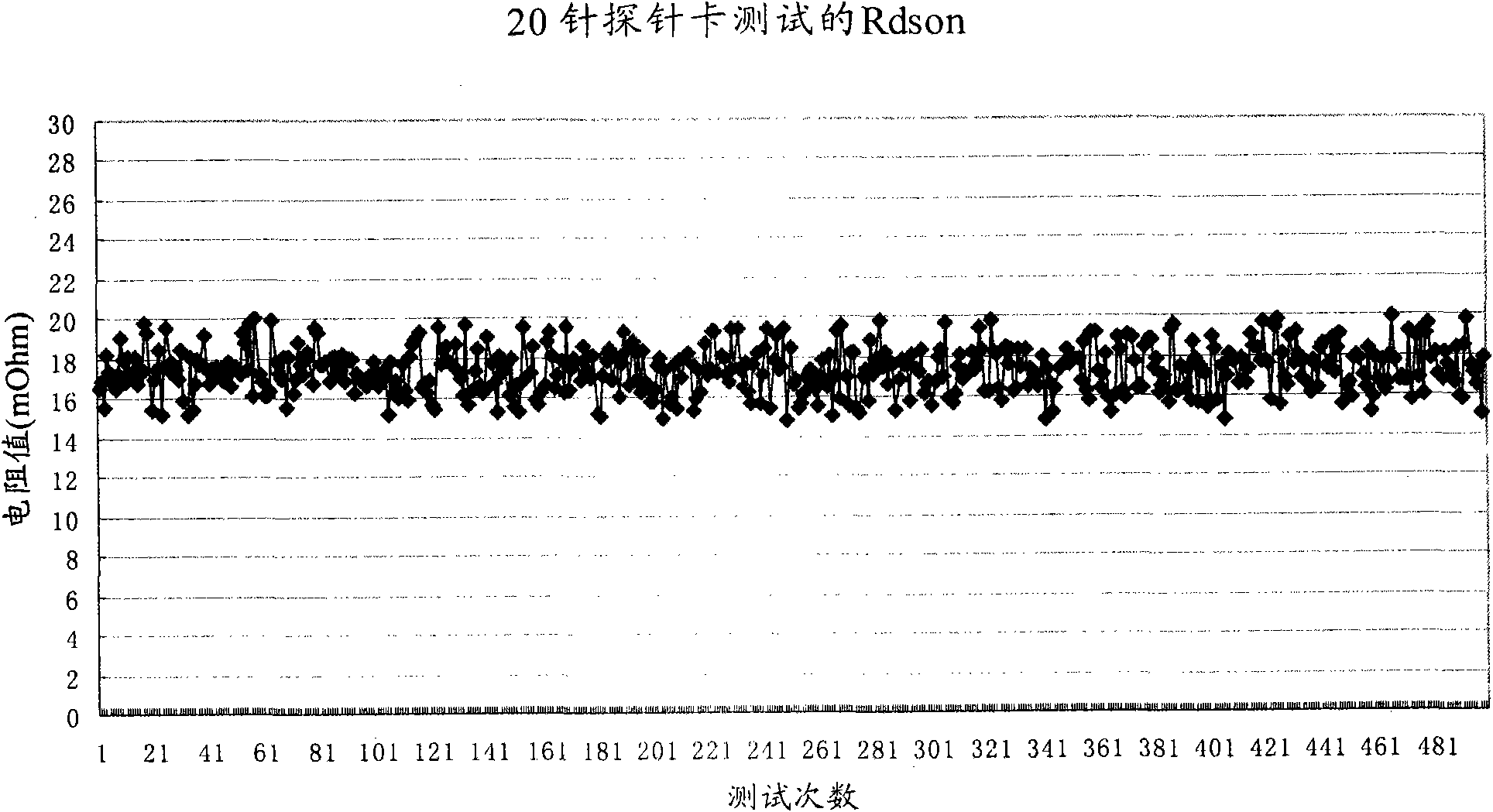

A technology of MOS devices and testing methods, which is applied in the direction of single semiconductor device testing, semiconductor/solid-state device testing/measurement, components of electrical measuring instruments, etc., and can solve the problem of large fluctuations in test conduction resistance and unstable test signals, etc. problem, to achieve the effect of reducing test signal interference, improving stability and accuracy, and improving stability and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0009] The method for testing a MOS device of the present invention is applied to testing the on-resistance of a wafer-level MOS device by using a probe card. According to the test requirements of different MOS devices, the probe card can choose probe cards with different pin numbers for testing. Several probes on the probe card are in contact with the source end of the MOS device, and a single needle is in contact with the gate of the MOS device as a gate loading probe. Each probe is connected with lead wires to lead out several connection points. The wiring points are distributed on the probe card, and are binding posts or wiring soldering points on the probe card. Use several probes on the probe card as source test probes, connect several connection points as source test probes for electrical continuity, and use several probes on the probe card as source load probes Needle, connect several connection points as source loading probes for electrical continuity. Since the co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com