Multichip package structure capable of arranging chips on pins

A multi-chip packaging and chip technology, applied to electrical components, electrical solid devices, circuits, etc., can solve the problems of limiting the number of stackable chips, being unable to stack chips, shortening the stackable height of chips, etc., to reduce the risk of line punching and avoid The effect of misalignment and reducing mold flow interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

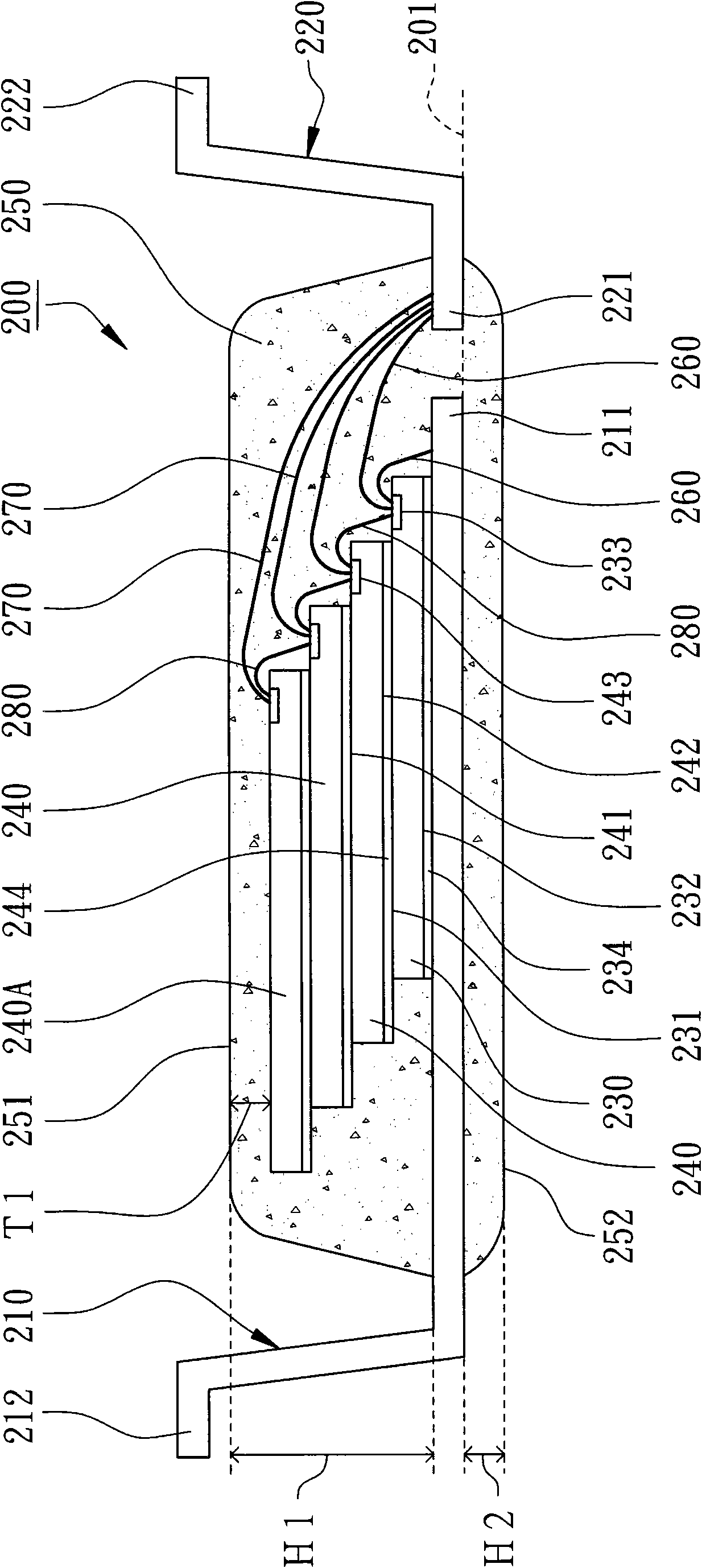

[0059] According to the first specific embodiment of the present invention, such as figure 2 As shown, a chip-on-lead multi-chip package structure 200 mainly includes two or more first leads 210 , a first chip 230 , one or more second chips 240 and an encapsulant 250 .

[0060] see figure 2 As shown, each first pin 210 has a first inner foot 211 and a first outer foot 212, wherein the "inner foot" is the part where the pin is sealed in the sealing body 250; the "outer foot" The finger pins extend outside the encapsulant 250 . These first pins 210 can belong to the same lead frame, which can be made of iron, copper or other metal materials, and have an appropriate thickness (about 0.125 mm or more), enough to carry the first chip 230 and the second chip. 240 structural strength. Preferably, the thickness of the first pins 210 may not be smaller than the thickness of the first chip 230 . Moreover, the first inner legs 211 are coplanar and fully submerged. In other words, t...

no. 2 Embodiment

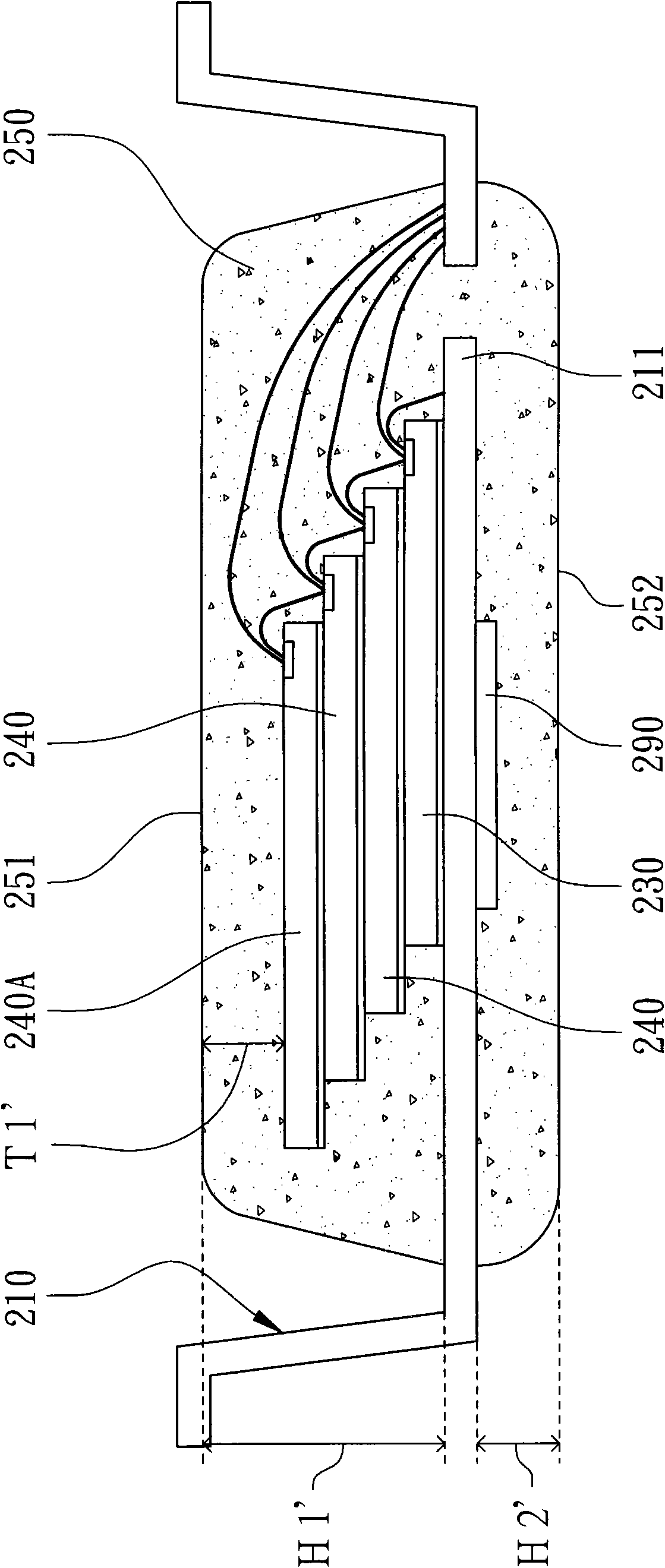

[0070] In a second specific embodiment of the present invention, see image 3 As shown, another multi-chip packaging structure with chips on pins is disclosed. Its main structure is roughly the same as that of the first embodiment of the present invention, so the component symbols of the first embodiment are used and will not be repeated. The multi-chip package structure mainly includes two or more first pins 210 , a first chip 230 , one or more second chips 240 and an encapsulant 250 . In this embodiment, the height distance H1' from the first inner legs 211 of the first pins 210 to the first surface 251 of the molding body 250 is approximately The height distance H2' of the two surfaces 252 is three times, and the number of the second chips 240 is appropriate, so that the height distance H2' from the first inner legs 211 to the second surface 252 of the encapsulant 250 is approximately the same The thickness T1 ′ of the encapsulant 250 from the first surface 251 to the near...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More