Safety JTAG module and method for protecting safety of information inside chip

A technology for internal information and protection chips, applied in computer security devices, internal/peripheral computer component protection, electronic digital data processing, etc. JTAG port protection measures failure and other problems, to achieve the effect of personalized management, avoid the risk of failure, and ensure security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] Specific embodiments of the present invention will be described below in conjunction with the accompanying drawings.

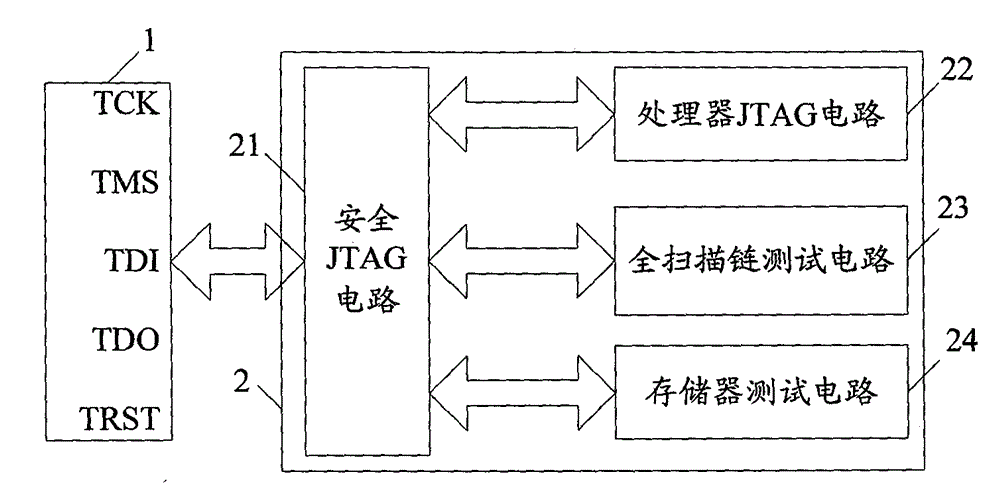

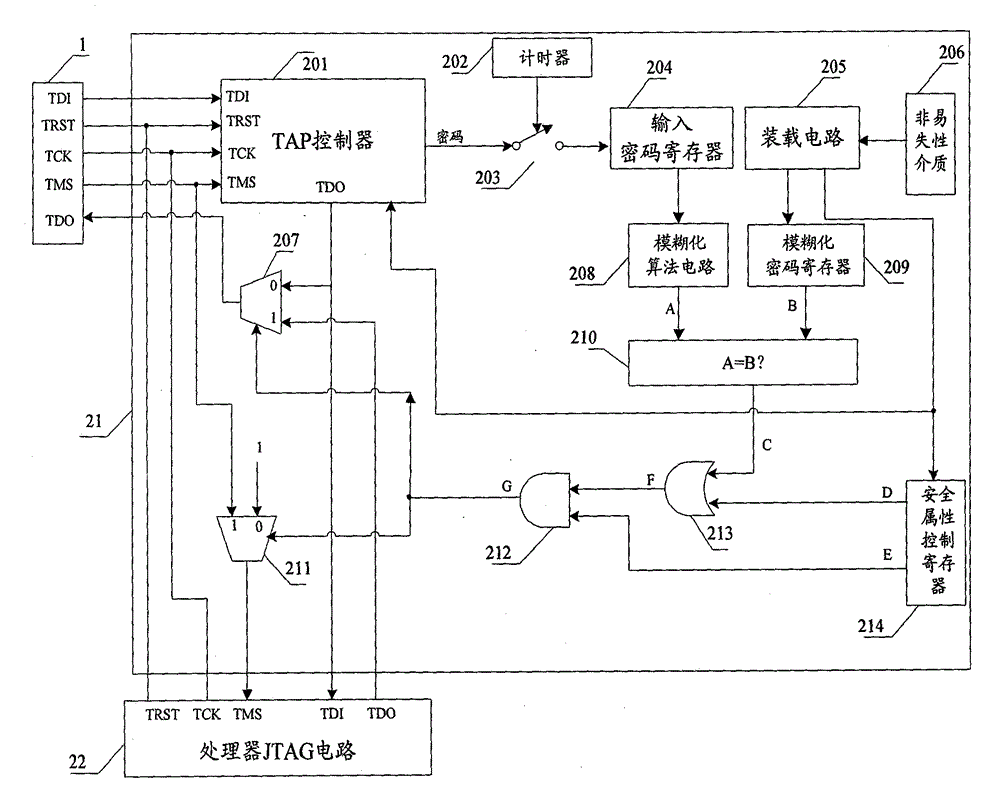

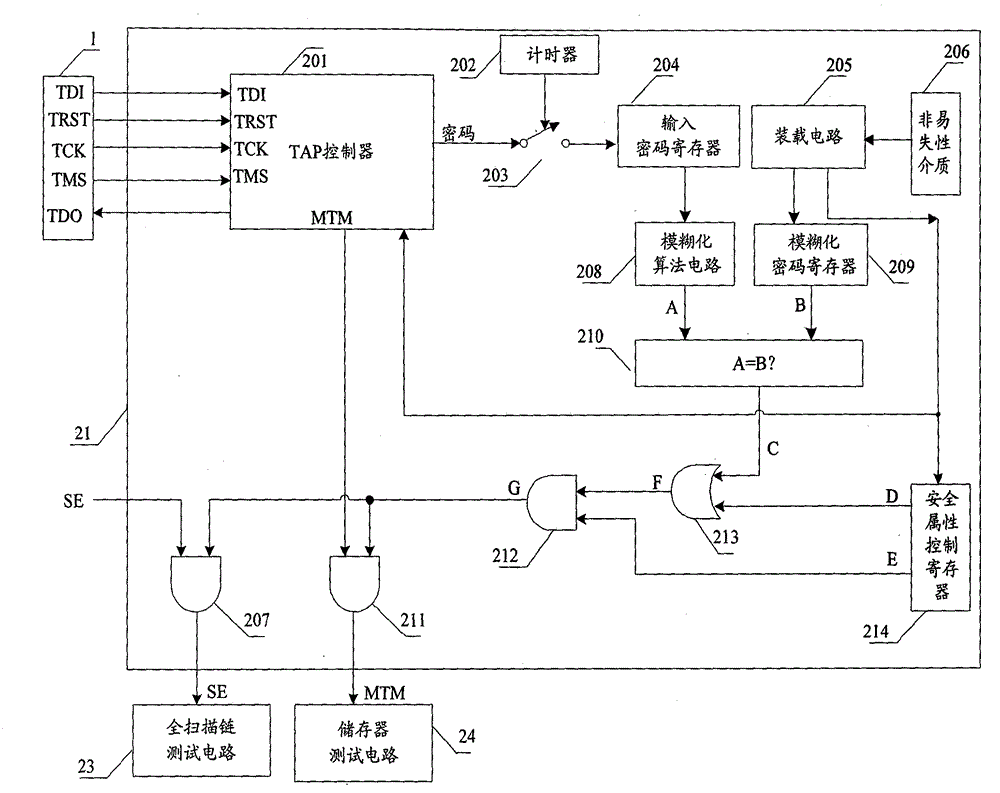

[0046] figure 1 It is a schematic diagram of the internal structure of the system chip disclosed in the present invention. A system on chip (System on Chip, SOC) 2 includes: a security JTAG (Join Test Action Group) circuit 21 , a processor JTAG circuit 22 , a full scan chain test circuit 23 and a memory test circuit 24 . Processor JTAG circuit 22, full scan chain test circuit 23 and memory test circuit 24 are objects (abbreviated as protection objects) that system chip 2 is protected by security JTAG circuit 21, only through the security permission of security JTAG circuit 21, the user can pass through JTAG port 1 accessing or starting the protection object, and realizing the test or debugging of the system chip 2 . Therefore, the present invention focuses on describing how the security JTAG circuit 21 implements security control on the processor JTAG...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More