System and method for fast cache-hit detection

A technology for error detection and cache state, applied in the field of storage systems, can solve problems such as inability to correct errors, missing cache, etc., and achieve the effect of reducing actual state and power usage, and reducing logic complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The making and using of the preferred embodiment of the invention are described in detail below. It should be appreciated, however, that the present invention provides many applicable inventive concepts that can be embodied in specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use the invention, and do not limit the scope of the invention.

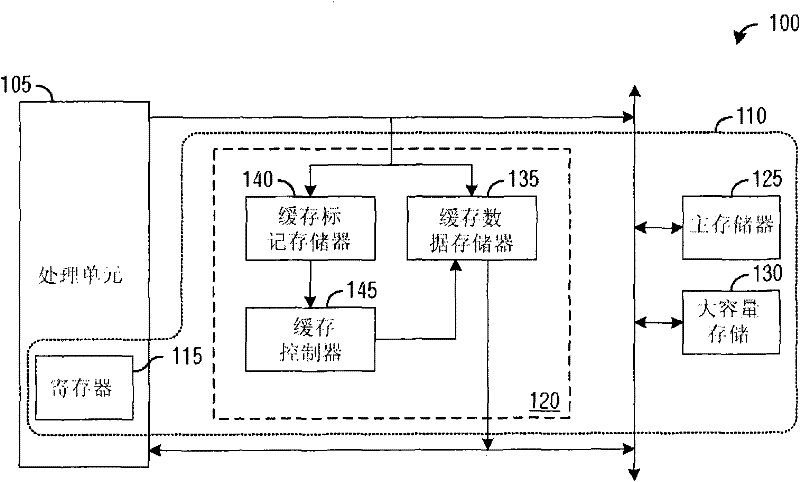

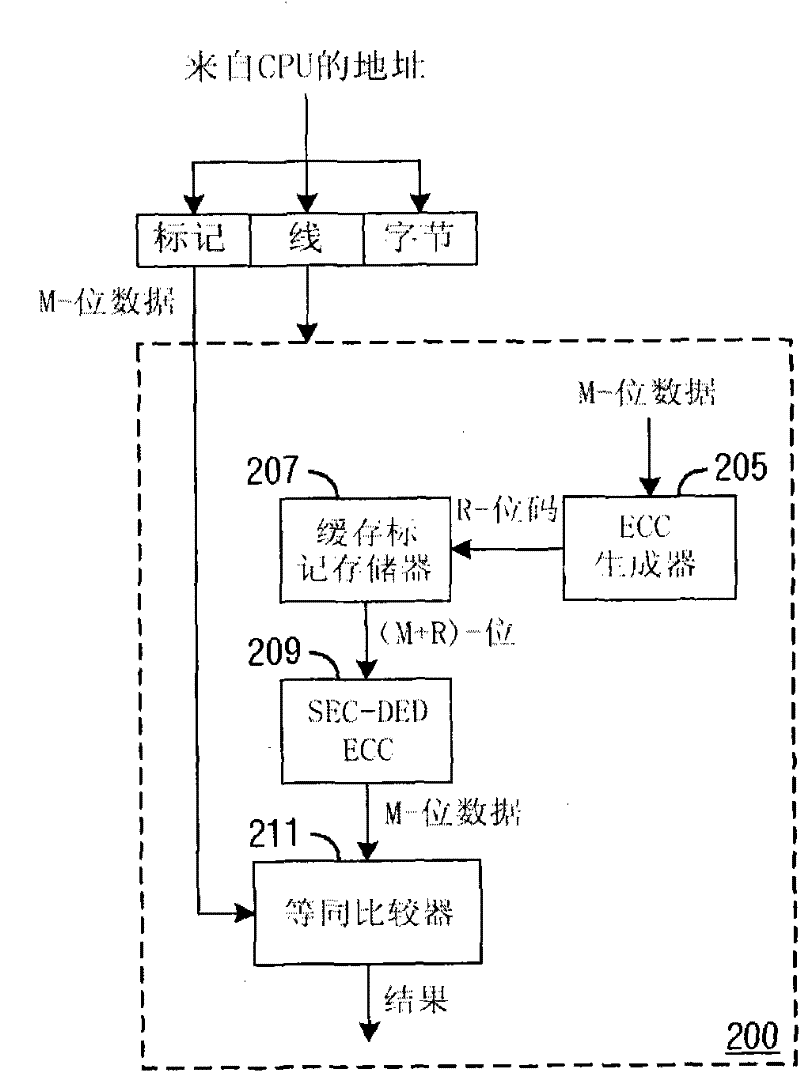

[0038] Embodiments will be described in the context of a computer system having a memory system that utilizes ECC, which provides single-bit error correction and double-bit error detection, and cache memories to help improve memory system performance. However, the present invention is also applicable to other computer systems having memory systems using ECC capable of correcting and detecting additional bit errors.

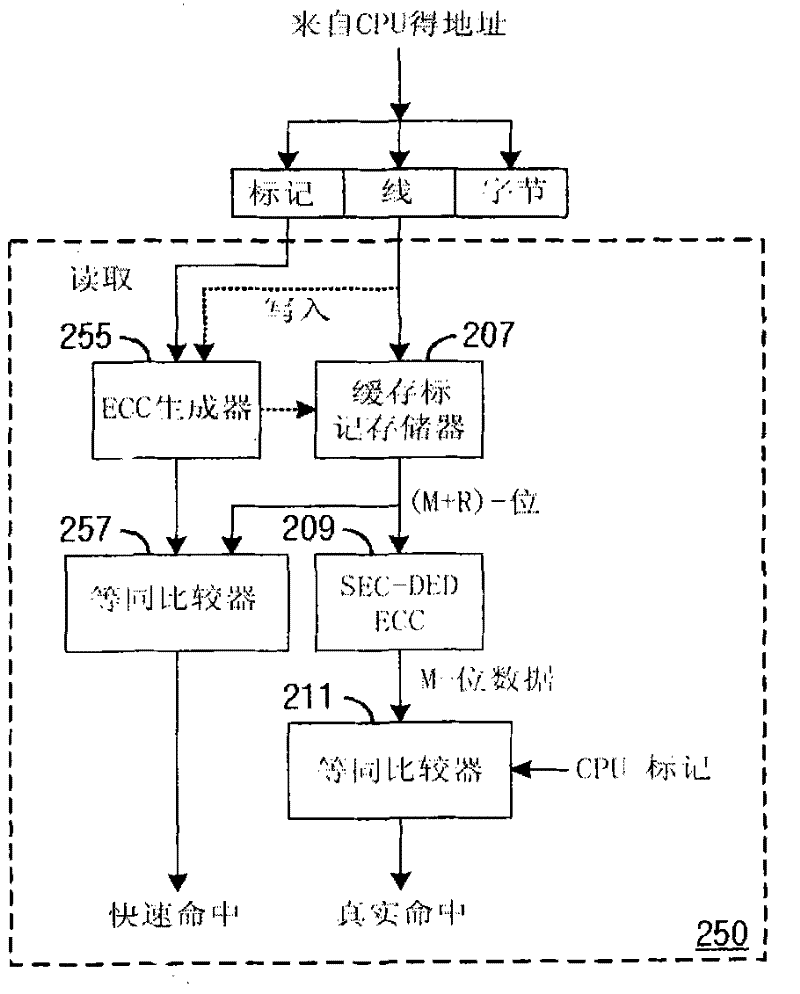

[0039] Figure 3a is a schematic diagram showing a detailed view of the cache access unit 300 . Such as Figure 3a As shown, cache access unit 300 may determin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More