Instruction execution method for vector complex multiplication operation and corresponding device

A technology of complex number multiplication and instruction execution, applied in the field of microprocessor architecture, can solve the problems of long pipeline series, instruction window control queue blockage, increase of processor area, etc., to save area and cost, avoid expansion, and avoid complexity degree of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

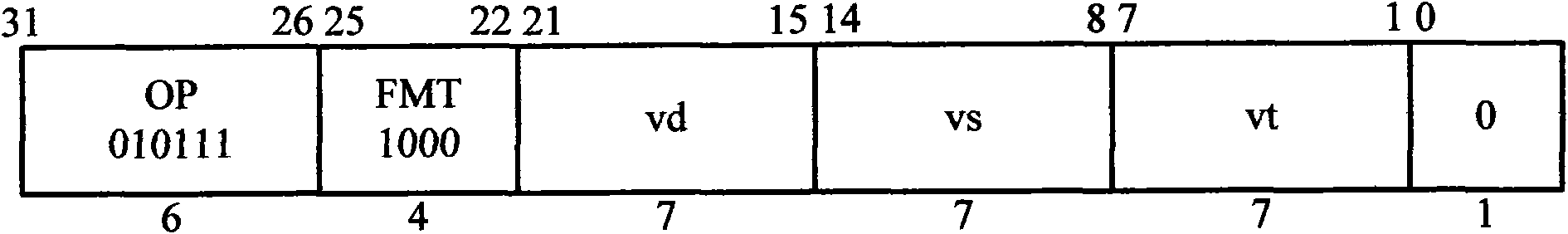

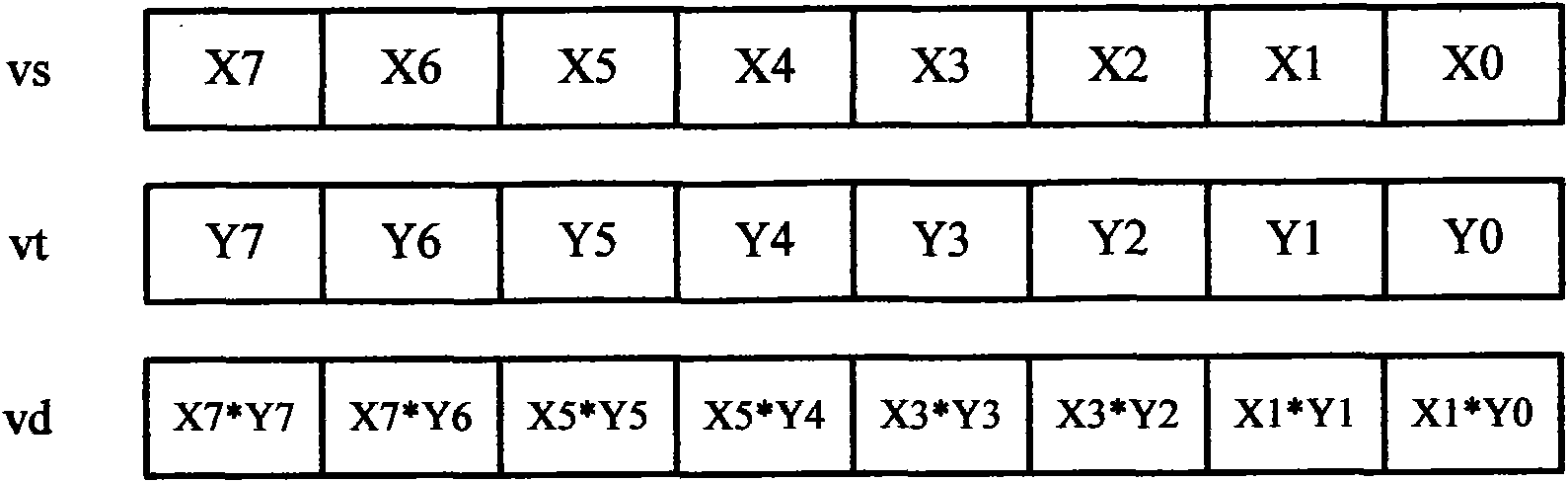

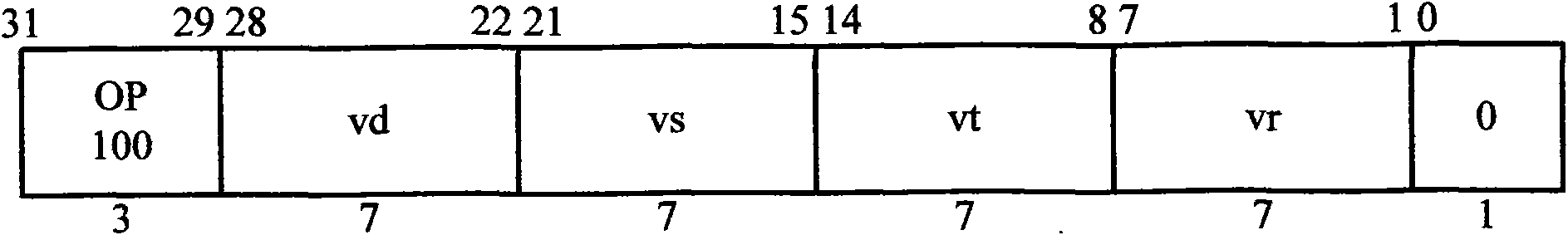

[0023] As mentioned above, the present invention aims to reduce the pipeline length and hardware implementation cost of complex vector multiplication operations, and its main idea is to use two instructions to pair to complete vector complex multiplication operations, wherein the first instruction performs vector complex multiplication The multiplication operation, the second instruction does the multiplication and addition operation of vector complex numbers. Also, the two instructions multiplex the vector multiply-accumulate functional unit, and two floating-point single precision and one floating-point double-precision multiplex one vector multiply-accumulate functional unit.

[0024] refer to Figure 9 Shown the block diagram of the vector multiplication and addition functional unit of the present invention, the operation of explaining the vector multiplication and addition functional unit in detail is as follows with the operand being 256 bits: every cycle transmits a vec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com