Integrated circuit SoC chip circuit structure capable of realizing power reduction and method thereof

A technology of integrated circuit and circuit structure, which is applied in the field of circuit structure of integrated circuit SoC chip to reduce power consumption, which can solve the problems that the leakage control cannot achieve the ideal effect, the battery cannot be expanded and the battery capacity is increased, and the control process can be achieved. Fast and convenient, stable and reliable working performance, and the effect of reducing static power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] In order to understand the technical content of the present invention more clearly, the following examples are given in detail.

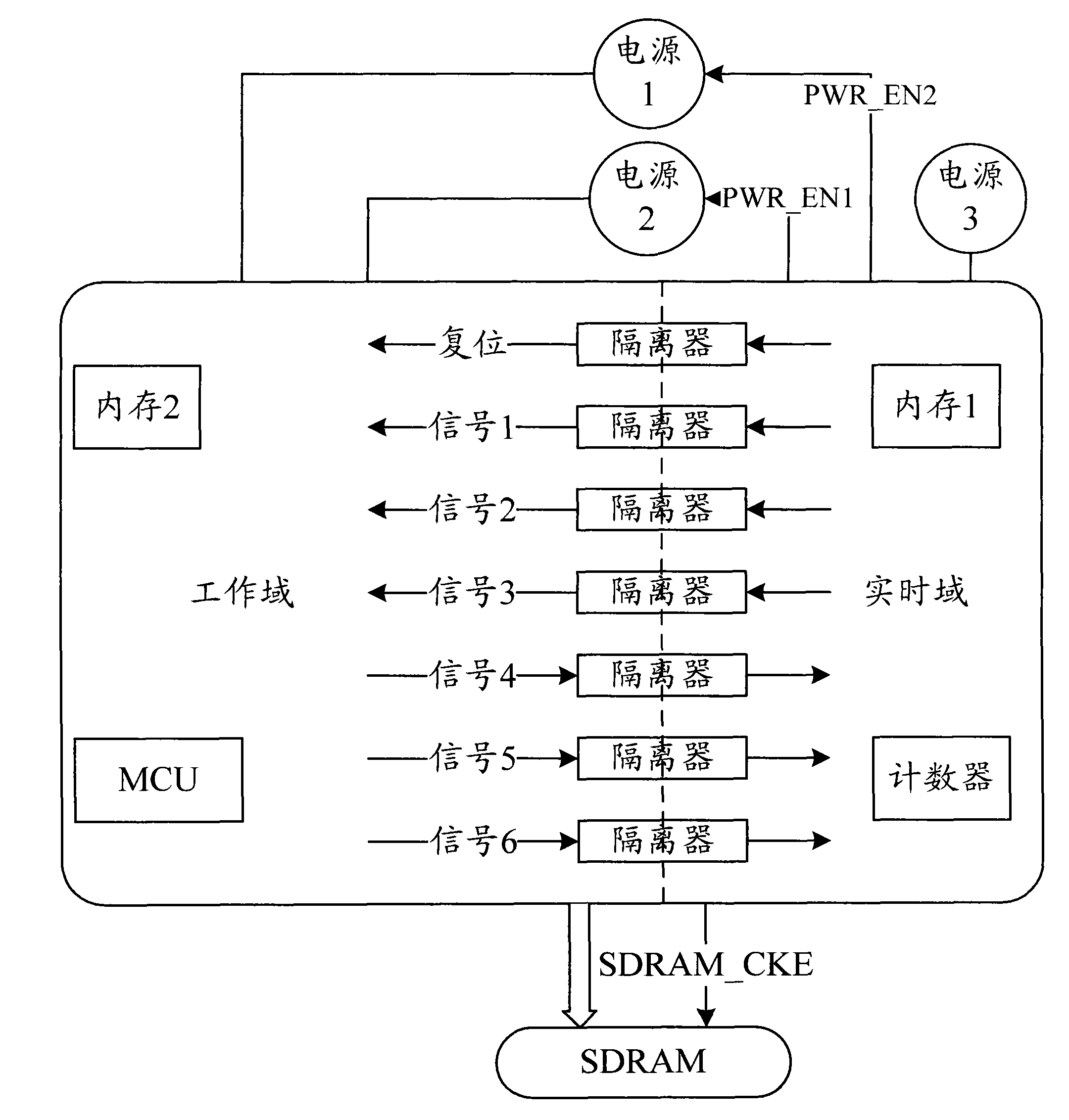

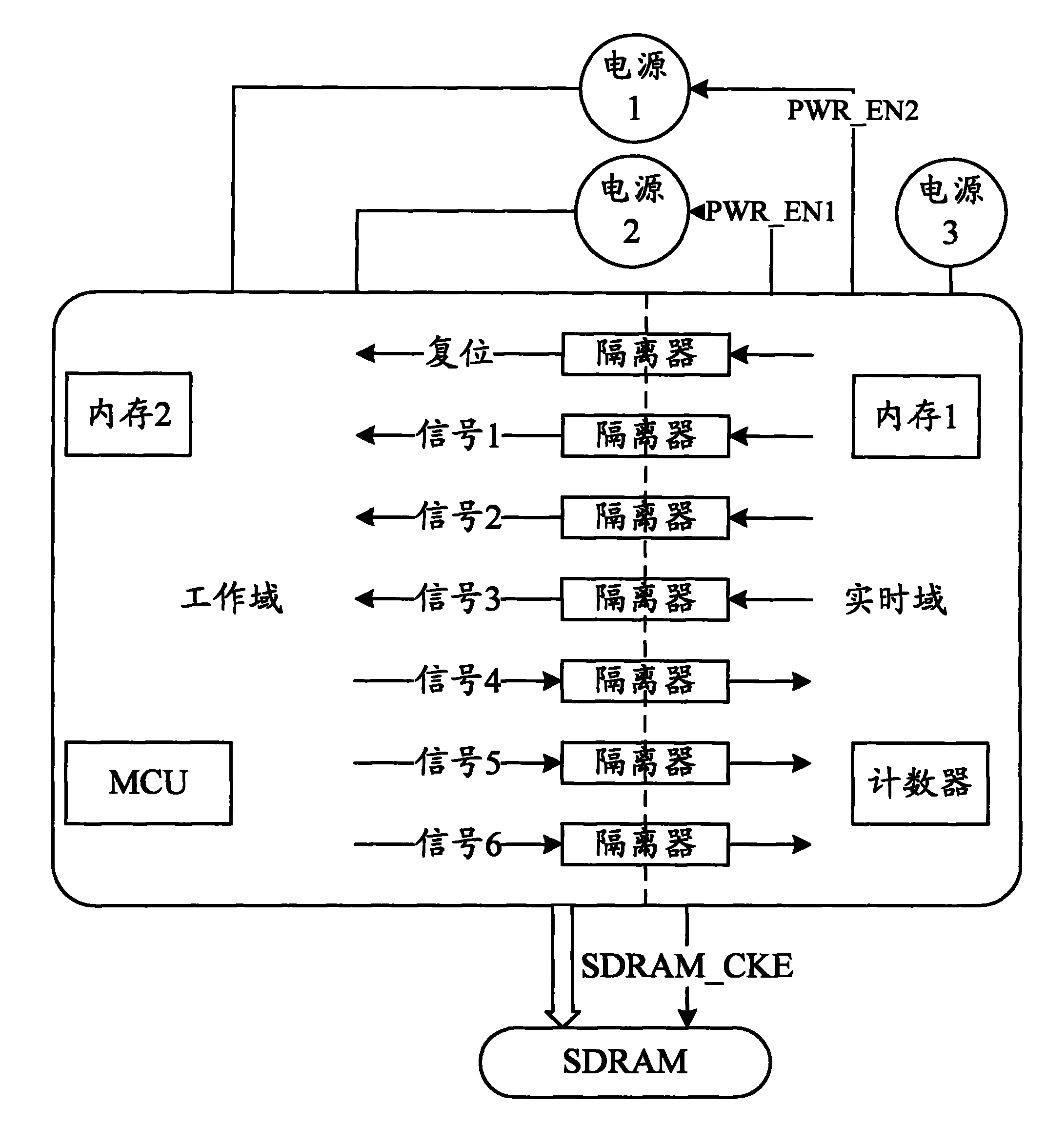

[0046] see figure 1 As shown, the integrated circuit SoC chip realizes the circuit structure of power consumption reduction, wherein, there is at least one working domain that cuts off power and at least one real-time domain that is always powered off in the said Soc chip, and said working domain An isolator is arranged between the real-time domain and the working domain and the real-time domain are respectively connected to external power supply.

[0047] Wherein, an isolator is also arranged between each of the work domains, the external power supply includes at least one work domain power supply and at least one real-time domain power supply, and the work domain is connected to the corresponding at least one work domain power supply , the real-time domain is connected to the corresponding real-time domain power supply; the described work ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More