Semiconductor chip package and quad flat non-pin package

A technology of leadless packaging and chip packaging, which is applied in the direction of semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., can solve the problem of high cost and achieve the effect of cost reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to make the above and other objects, features, and advantages of the present invention more obvious and understandable, the following specifically enumerates the preferred embodiments with accompanying drawings, which are described in detail as follows. It should be noted that the following embodiments are only used to illustrate the purpose of the present invention, and are not a limitation of the present invention. The scope of rights of the present invention shall be subject to the claims.

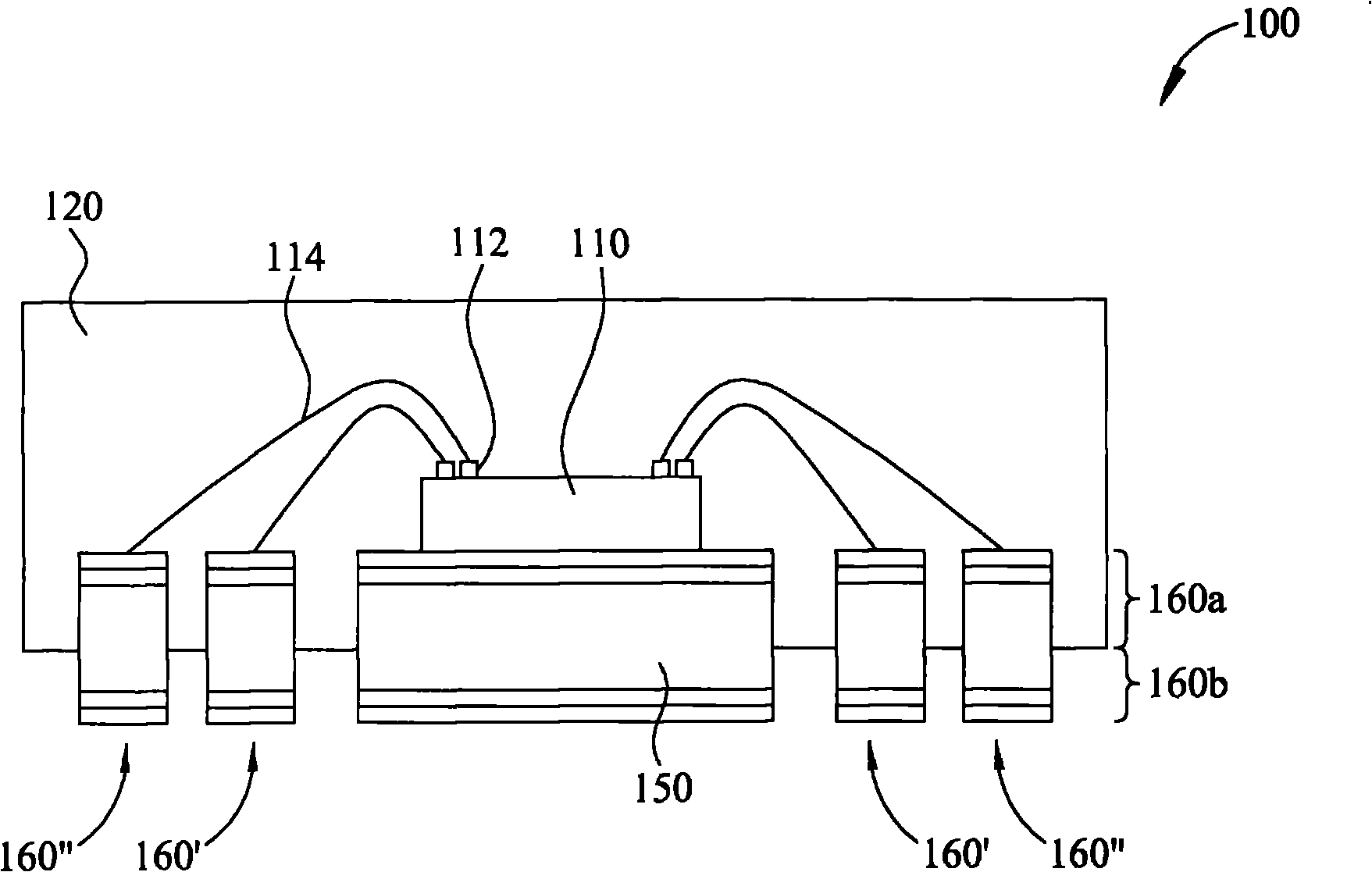

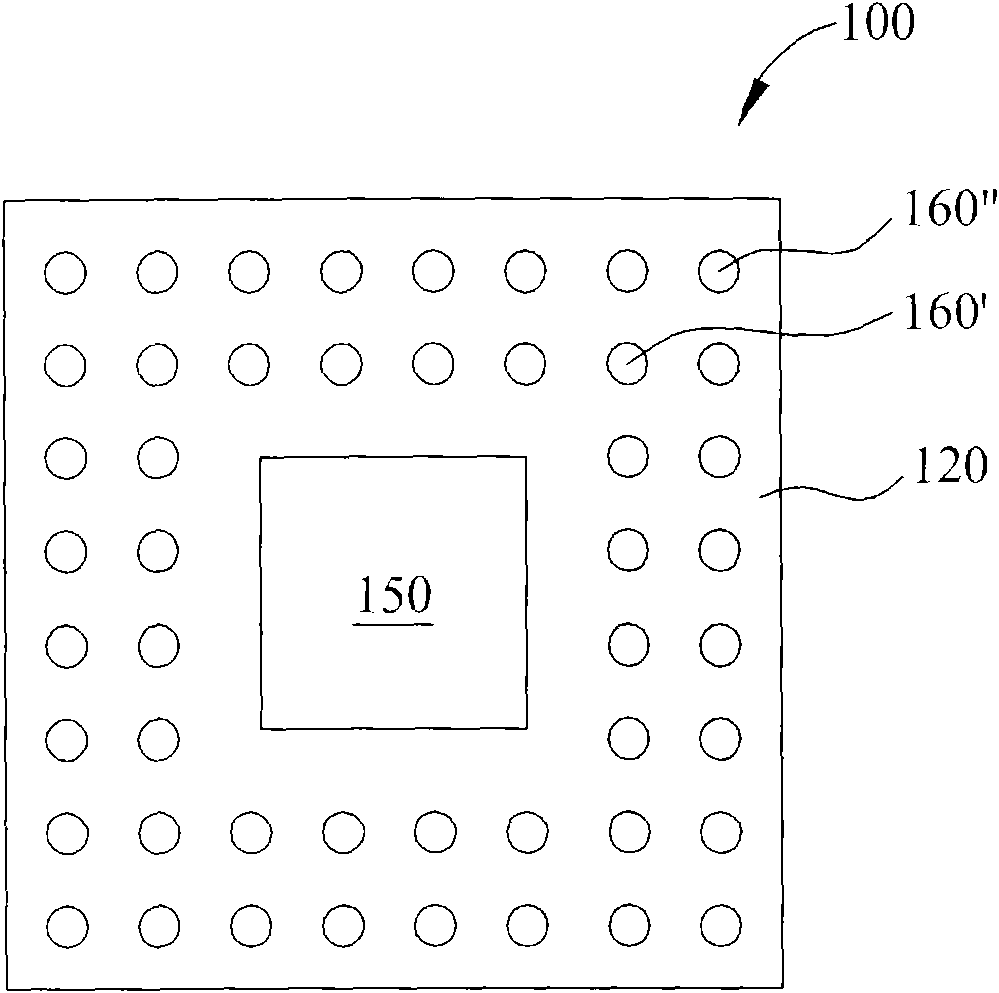

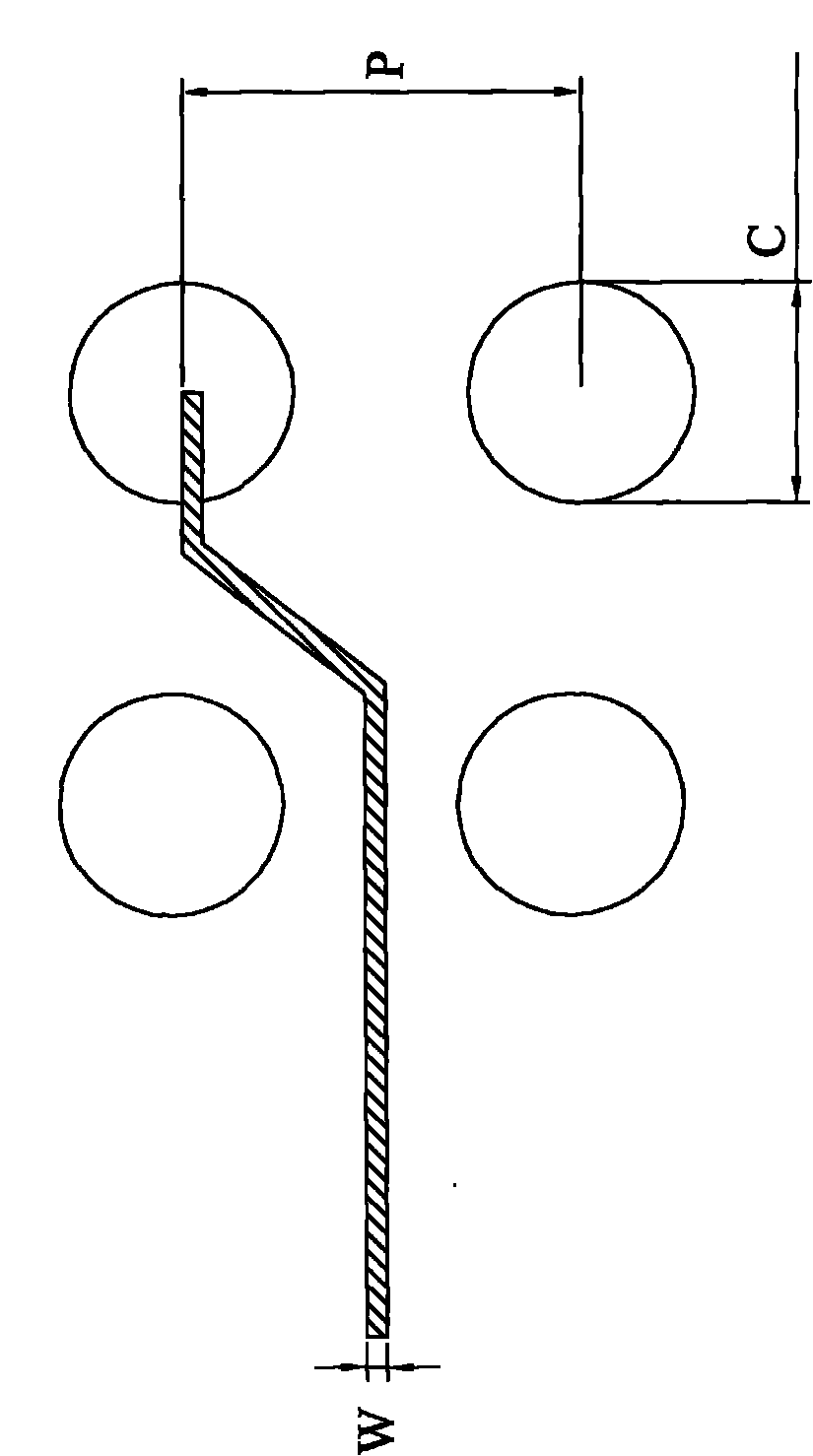

[0024] Figure 4 It is a cross-sectional view of a QFN package 200 according to an embodiment of the present invention. Figure 5 for Figure 4 The bottom view of the QFN package 200 shown. Such as Figure 4 with Figure 5 As shown, the QFN package 200 includes a chip 210 attached to a bare chip pad 250; a plurality of internal connection pads 260 are arranged around the periphery of the bare chip pad 250; and a plurality of middle connection pads 260 ', are arranged aroun...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More