Clock pulse signal generation method

A clock pulse and signal generation technology, applied in the field of clock pulse signal generation, can solve problems such as insufficient pixel charging rate, waveform distortion, pixel P loss of brightness, etc., and achieve the effect of improving display quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

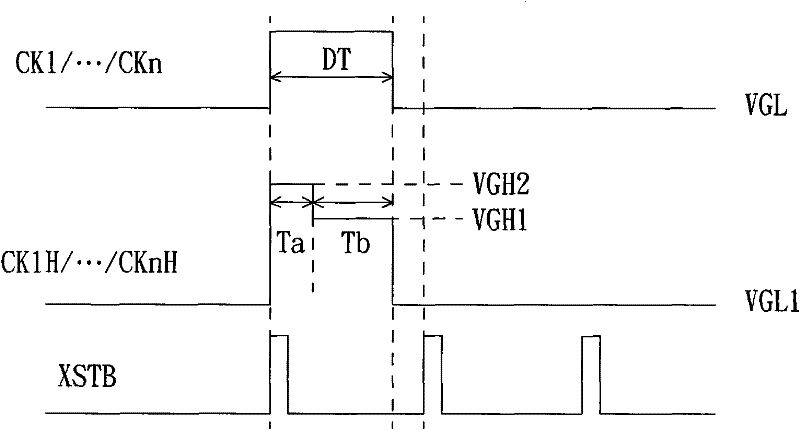

[0053] see image 3 , which shows a timing diagram of multiple signals related to a method for generating a clock pulse signal according to an embodiment of the present invention. The method for generating the clock pulse signal in this embodiment is suitable to be implemented in a display, such as an active matrix display using an on-array gate driving circuit and / or a half-source driving structure, but the present invention is not limited thereto. The following will combine image 3 Each step of the method for generating a clock pulse signal in this embodiment will be described in detail.

[0054] First, at least one initial clock pulse signal CK1˜CKn is provided, where n is a positive integer. image 3 The waveform of any one of the initial clock pulse signals CK1~CKn is shown in , the duty period DT of the initial clock pulse signals CK1~CKn in each frequency period (not marked) has an initial high potential VGH, and in this frequency period The non-responsible period (...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More