Clock delay compensation device and clock delay compensation synchronization method

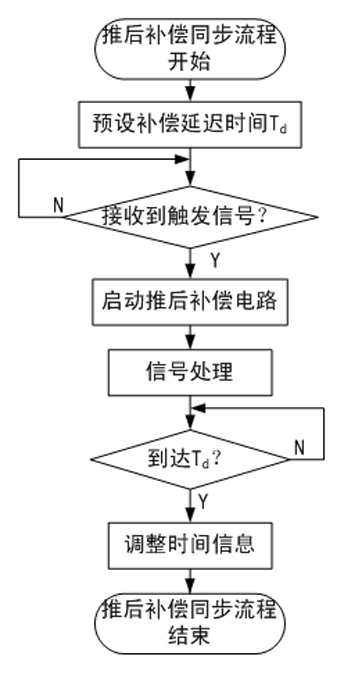

A post-compensation and clock technology, which is applied in the field of clock synchronization, can solve the problems of large error between the calibration clock and the standard clock, difficult measurement and estimation of time stamp error signal processing time, time stamp error, etc., and achieve high clock synchronization accuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

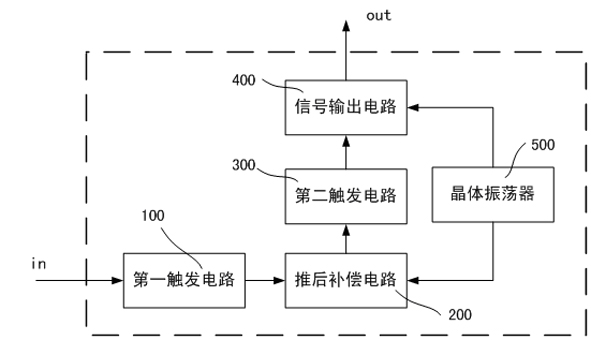

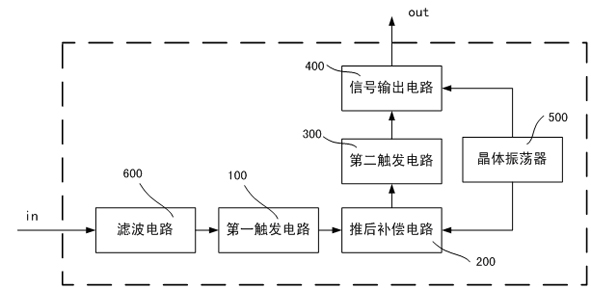

[0031] As an aspect of the present invention, such as figure 1 As shown, the clock delay compensation device includes a first trigger circuit 100 , a delay compensation circuit 200 , a second trigger circuit 300 , a crystal oscillator 400 , and a time output circuit 500 . The crystal oscillator 400 is connected to the time output circuit 500 and the delay compensation circuit 200 respectively, and the delay compensation circuit 200 is also connected to the first trigger circuit 100 and the second trigger circuit 300 respectively, and the second trigger circuit 300 is also connected to the time output circuit 500 connected. Among them, the crystal oscillator 400 is used to provide a stable clock frequency to the ti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More