Dynamic random access memory (DRAM)

A memory and storage unit technology, applied in the field of memory, can solve problems such as multi-storage unit area, low noise immunity, and DRAM memory process difficulties, and achieve the effect of reducing free area, low noise immunity, and good use of storage unit area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The DRAM memory provided by the present invention has 7F 2 Storage unit, where F represents the feature size (featue size), 7F 2 Indicates the area of each storage unit. The DRAM memory of the present invention will be described in detail below with reference to the accompanying drawings.

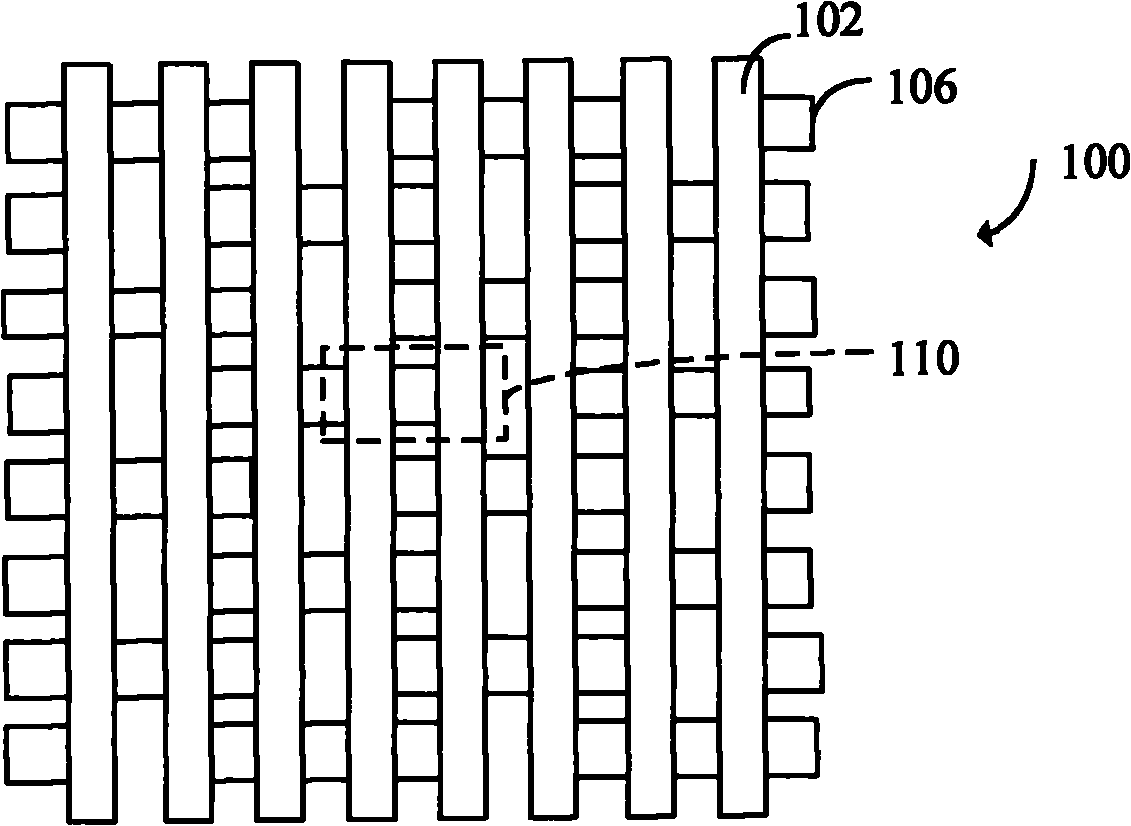

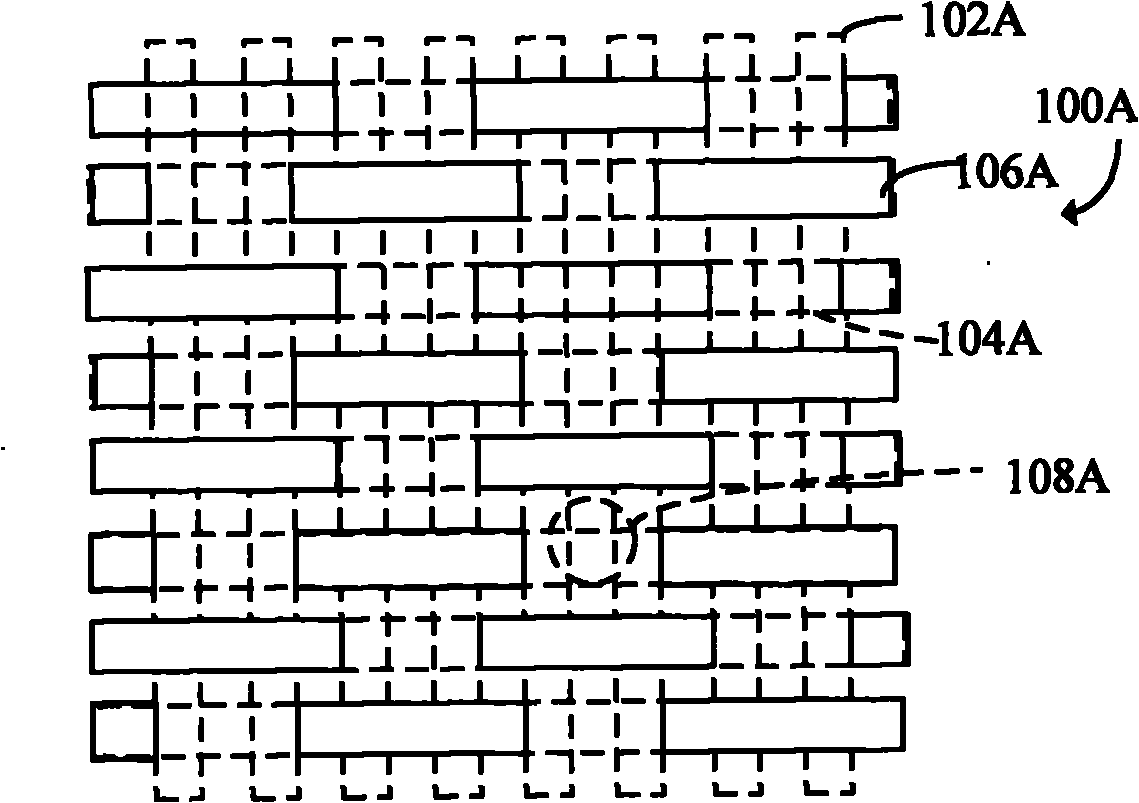

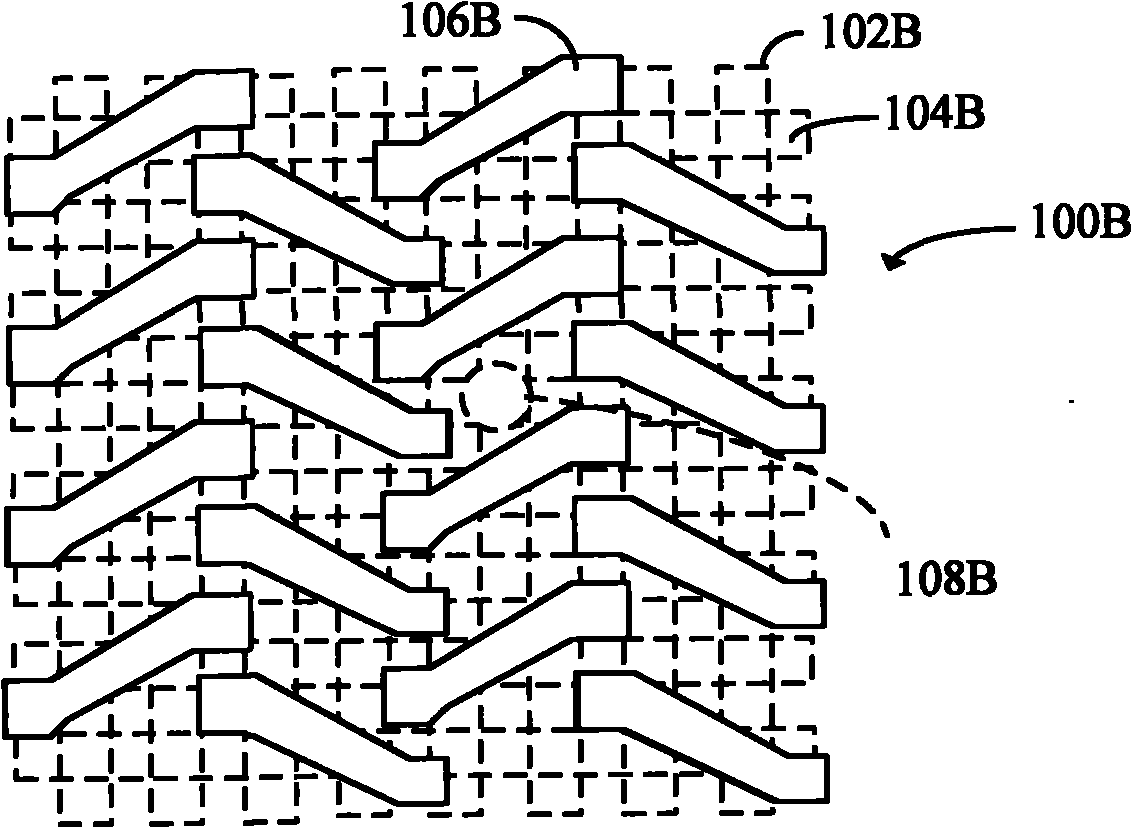

[0030] refer to image 3 It is a schematic diagram of the local layout of the DRAM memory of a specific embodiment of the present invention, while referring to Figure 4 for image 3 A partial layout diagram of the shown DRAM memory showing the location of the active area. The memory 300 includes a plurality of memory cells 302, an active area 304, word lines 306 arranged in parallel and equally spaced, and bit lines 308 arranged in parallel and equally spaced and perpendicular to the word lines. Wherein, the area of each storage unit 302 is 7F 2 ; The pitch Lw between the word lines 306 is 2F, and the pitch Lb between the bit lines 308 is The storage unit area (cell_size...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More