Digital edge aligner for a PFD

A technology of frequency and phase detectors and aligners, which is applied to the automatic control of power and electrical components, and can solve problems such as precise alignment and difficult control of pulses

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] In order to make the objectives, technical solutions, and advantages of the present invention clearer, the embodiments of the present invention will be described in further detail below in conjunction with the accompanying drawings.

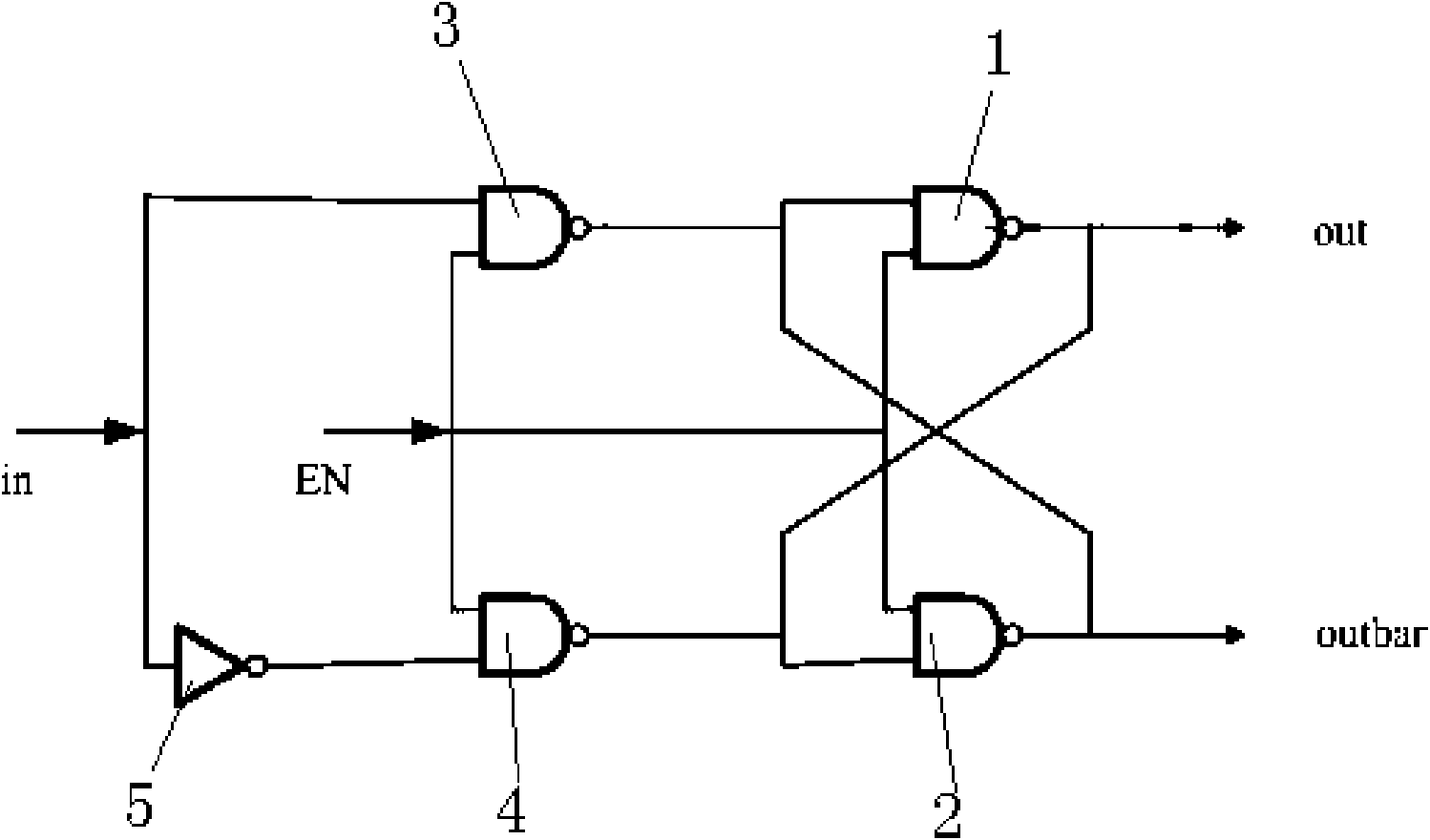

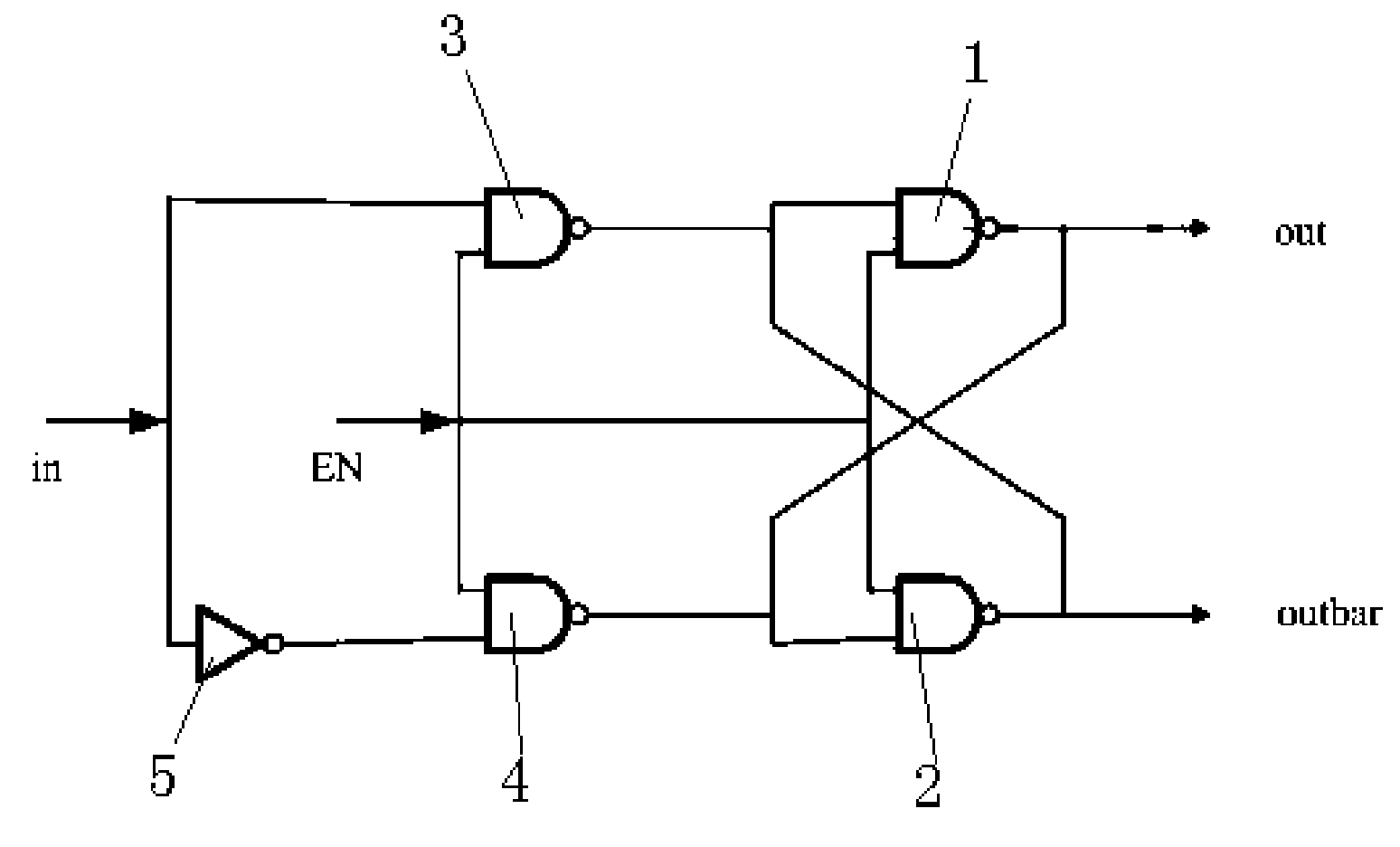

[0014] The present invention is a digital edge aligner for frequency phase detector. The digital edge aligner includes a flip-flop composed of basic logic gates, an inverter and a pair of NAND gates, which are connected to each other; It contains at least a pair of data input terminals, and can also include another control terminal. The flip-flop converts a signal into two pairs of inverted signals whose edges are aligned.

[0015] Such as figure 1 As shown, the pair of NAND gates is composed of 4 NAND gates, the 4 NAND gates are the first NAND gate 1, the second NAND gate 2, the third NAND gate 3, and the fourth NAND gate. Gate 4; the output terminal of the first NAND gate 1 is connected to the first input terminal of the second NAND gate 2,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More