Manufacturing method of memory

A manufacturing method and memory technology, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of difficulty, affect the size of the contact window, damage the first group of spacers, etc., and achieve good electrical insulation, good Effects of Component Properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to make the above-mentioned features and advantages of the present invention more comprehensible, the following specific embodiments are described in detail together with the accompanying drawings.

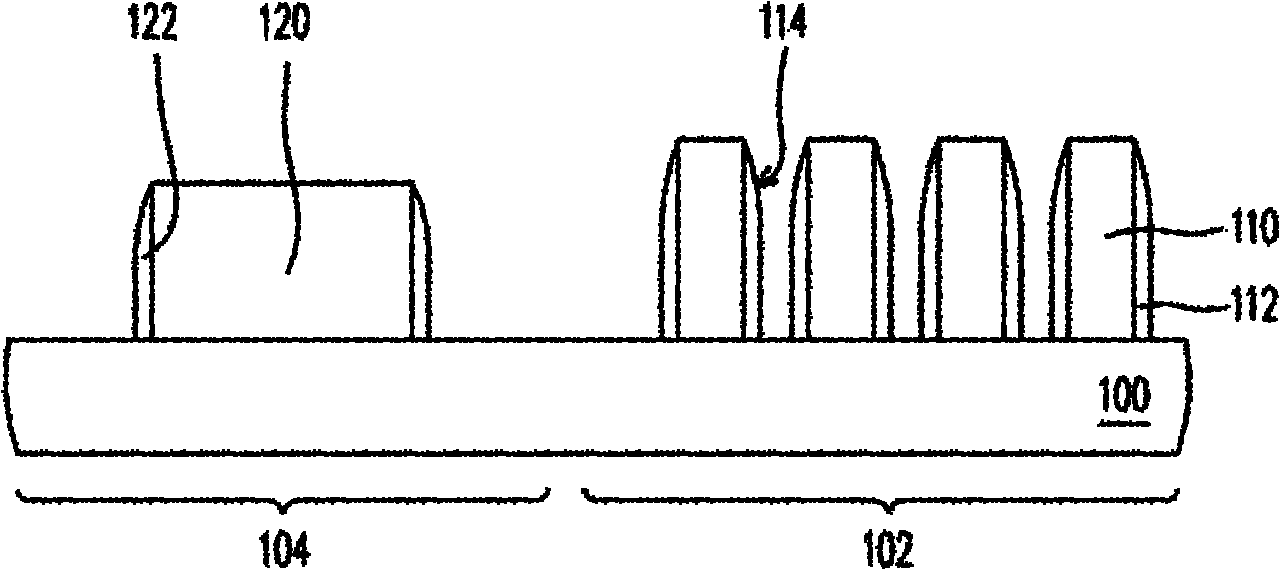

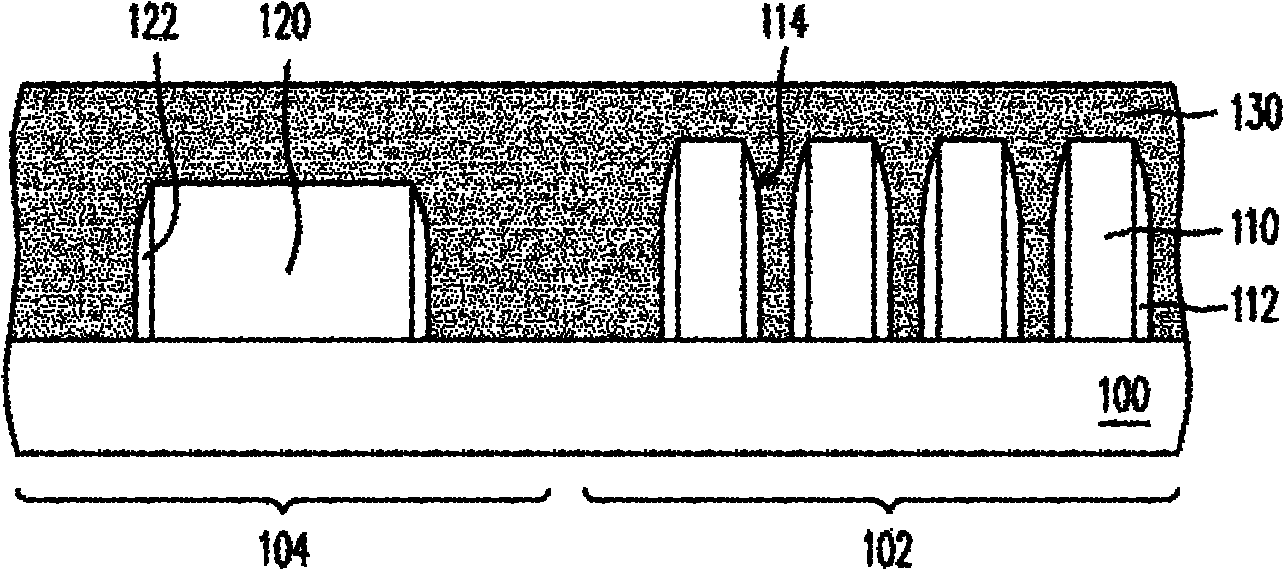

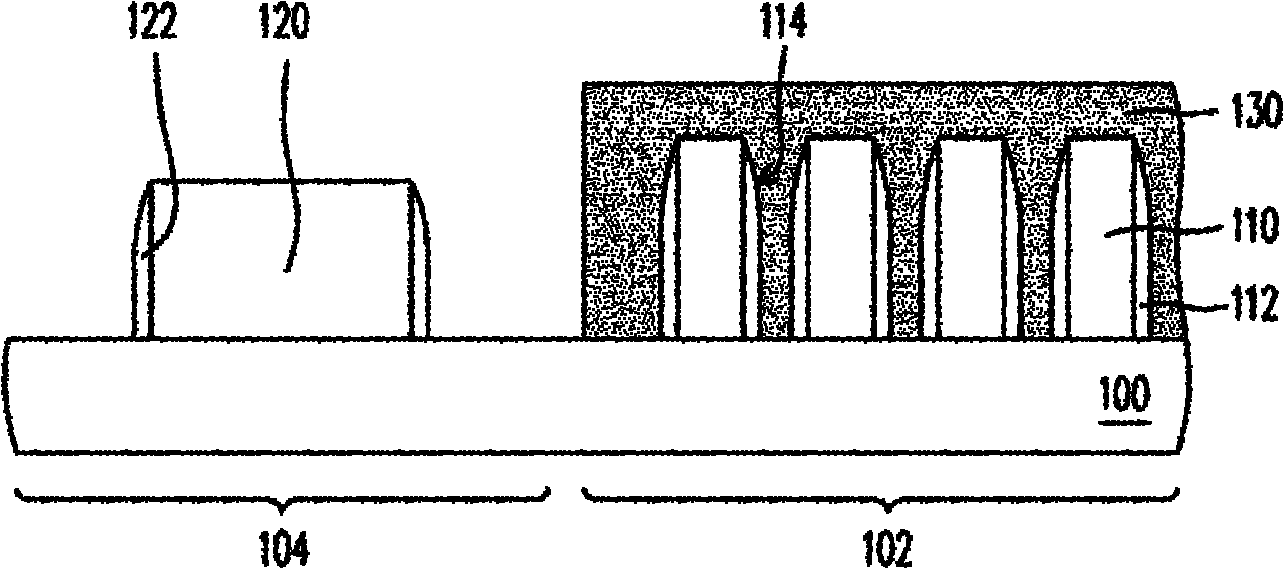

[0027] Figure 1A to Figure 1I is a schematic cross-sectional flow diagram of a manufacturing method of a memory according to an embodiment of the present invention, Figure 2A and Figure 2B respectively Figure 1A and Figure 1F The top view schematic diagram of the storage cell area, where Figure 1A and Figure 1F The storage cell area of Figure 2A and Figure 2B A schematic sectional view along line A-A', Figure 2A and Figure 2B The illustration of the spacer is omitted.

[0028] Please also refer to Figure 1A and Figure 2A , providing a substrate 100, the substrate 100 includes a memory cell region 102 and a peripheral region 104, a plurality of gates 110, 120 have been formed on the substrate 100, and first spacers 112, 122 are formed on the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More