Phase lock loop (PLL) device and control method thereof

A phase-locked loop and phase-locked technology, applied in the direction of automatic power control, electrical components, etc., can solve the problems of slowing down the system speed and redundancy, and achieve the effect of speeding up the speed of locking frequency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

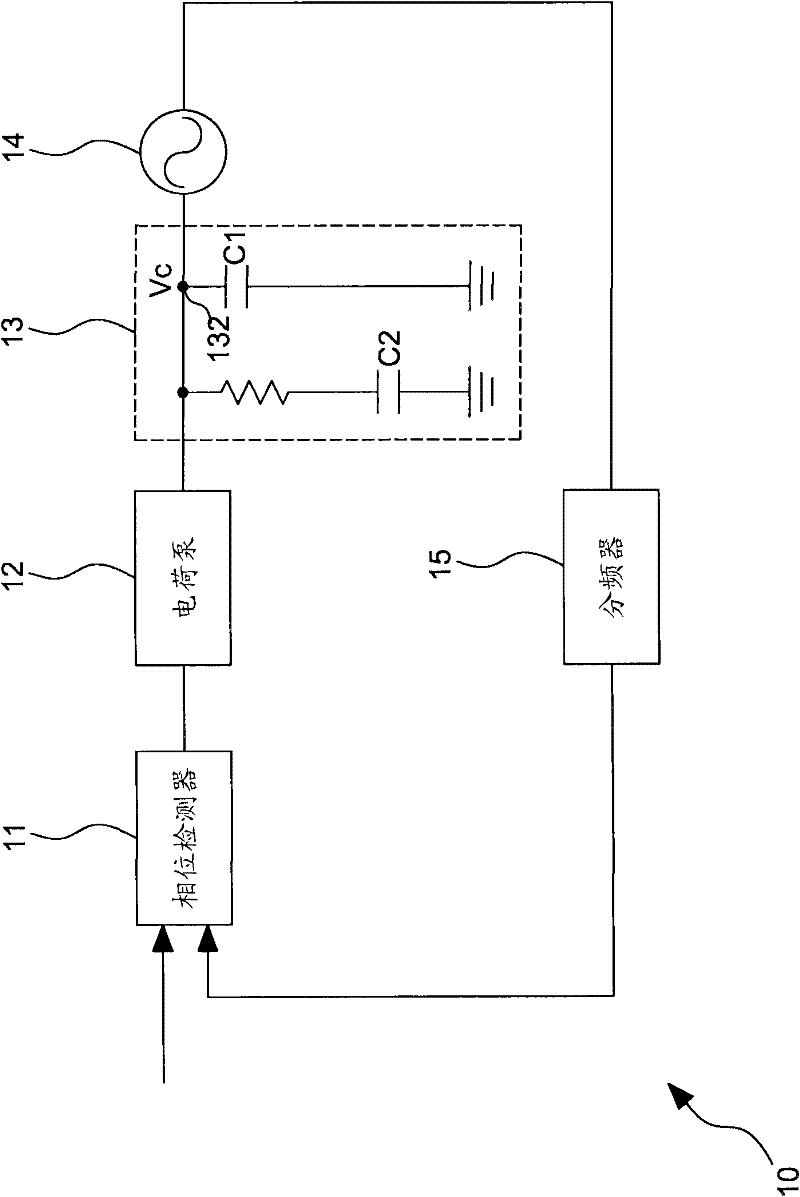

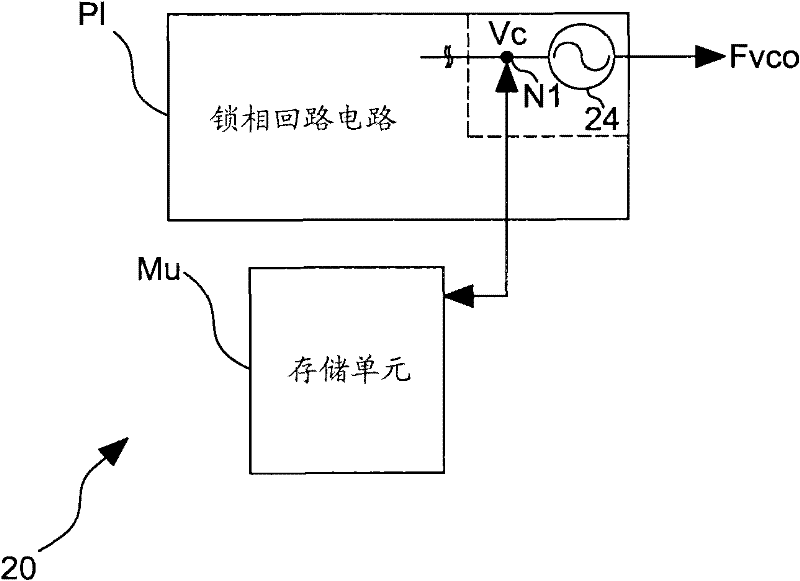

[0037] Figure 2A is a schematic diagram of an embodiment of a phase-locked loop device according to the present invention. The PLL device 20 can be a frequency generating device or a circuit that stores a control signal (voltage, current, etc.) and locks the frequency of the output clock signal. The phase-locked loop device 20 includes a phase-locked loop circuit P1 and a storage unit Mu. The phase-locked loop circuit P1 generates a phase-locked clock signal Fvco according to the control voltage Vc. When the phase-locked loop circuit P1 is activated, the storage unit Mu An initial signal is provided to the phase-locked loop circuit, so that the control voltage Vc is rapidly increased to a preset value. The detailed operation mode of this embodiment is described as follows:

[0038] The phase-locked loop circuit P1 includes a voltage-controlled oscillator 24 that outputs a phase-locked clock signal Fvco with a stable frequency according to the control voltage Vc. It should b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com