Emulation validation method of reading operation function of memory

A technology of simulation verification and operation function, applied in the direction of software simulation/interpretation/simulation, software testing/debugging, program control devices, etc., can solve the problems affecting the verification efficiency of memory read operation function, etc., so as to improve the simulation verification efficiency and ensure the accuracy sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

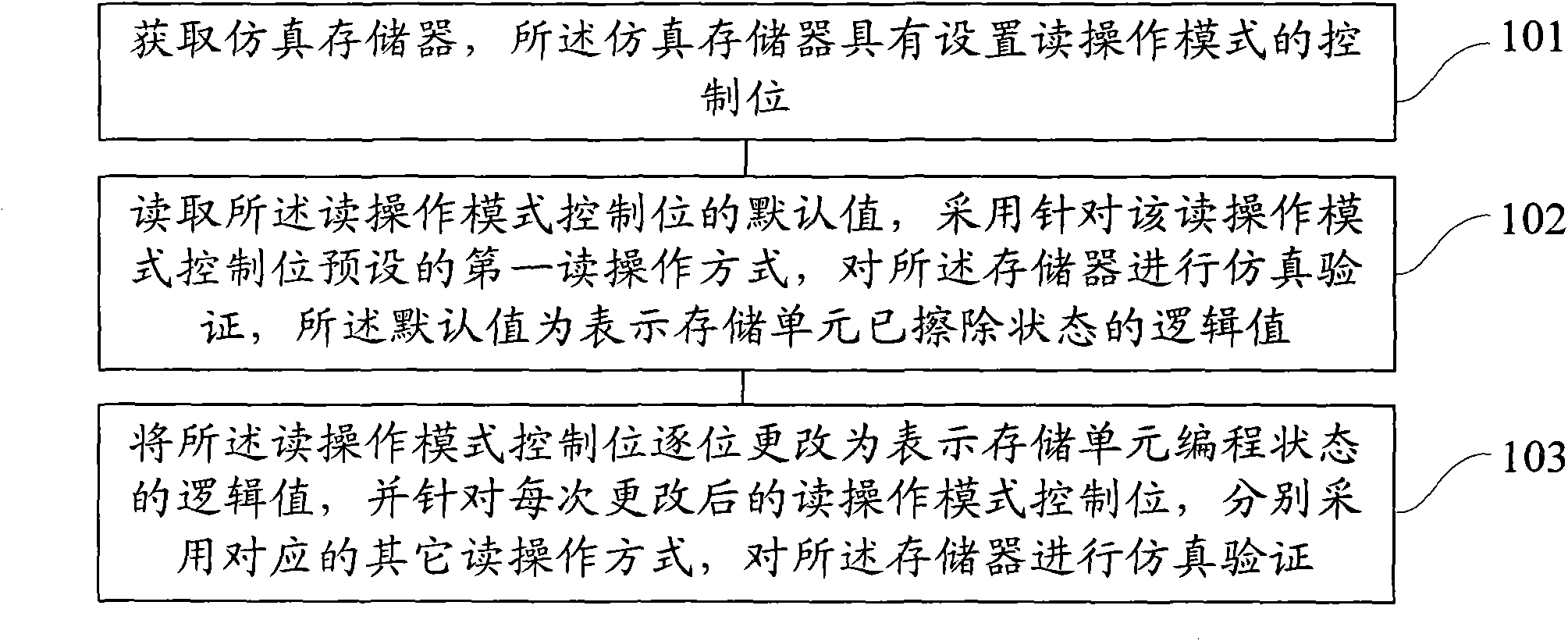

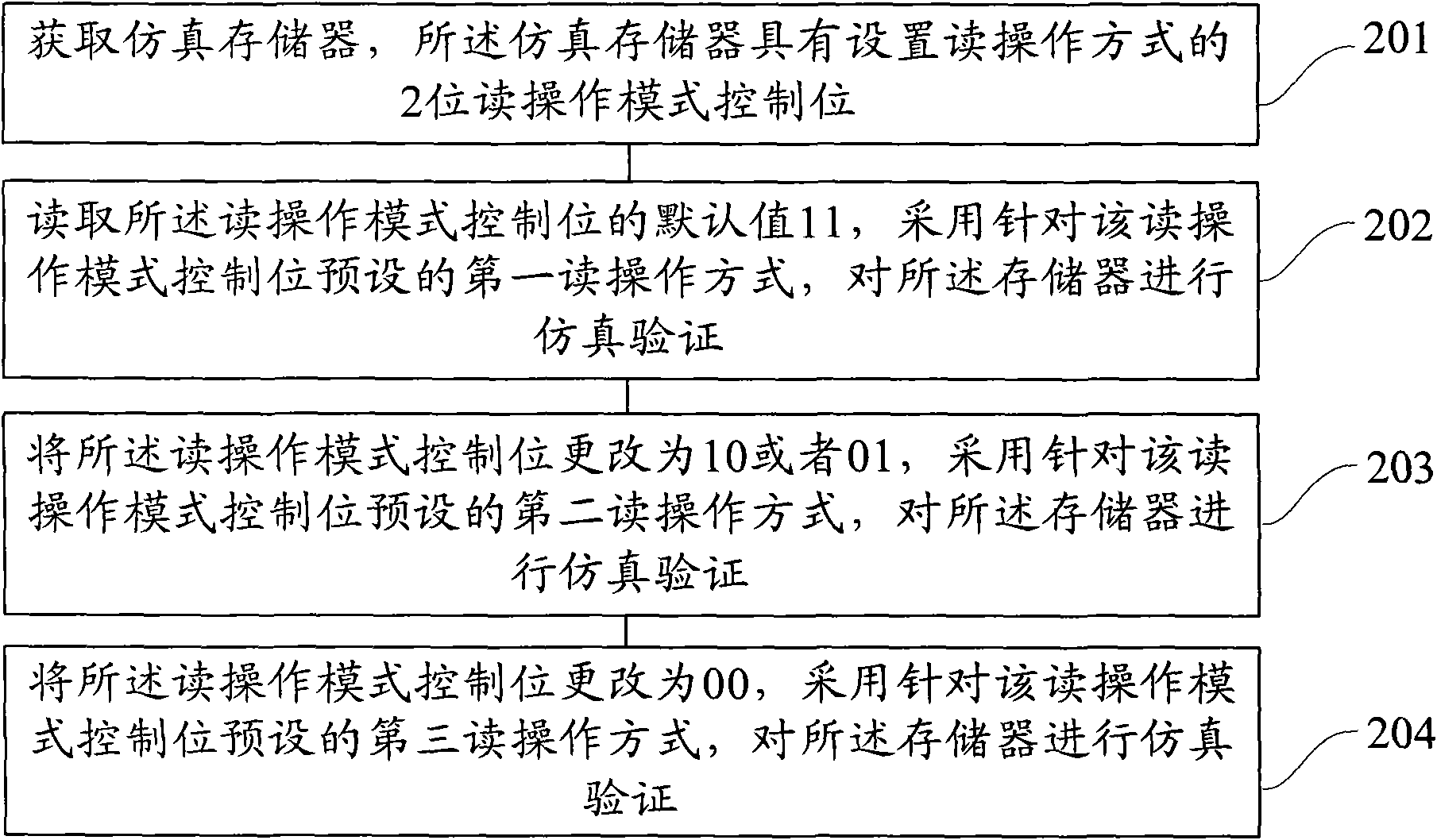

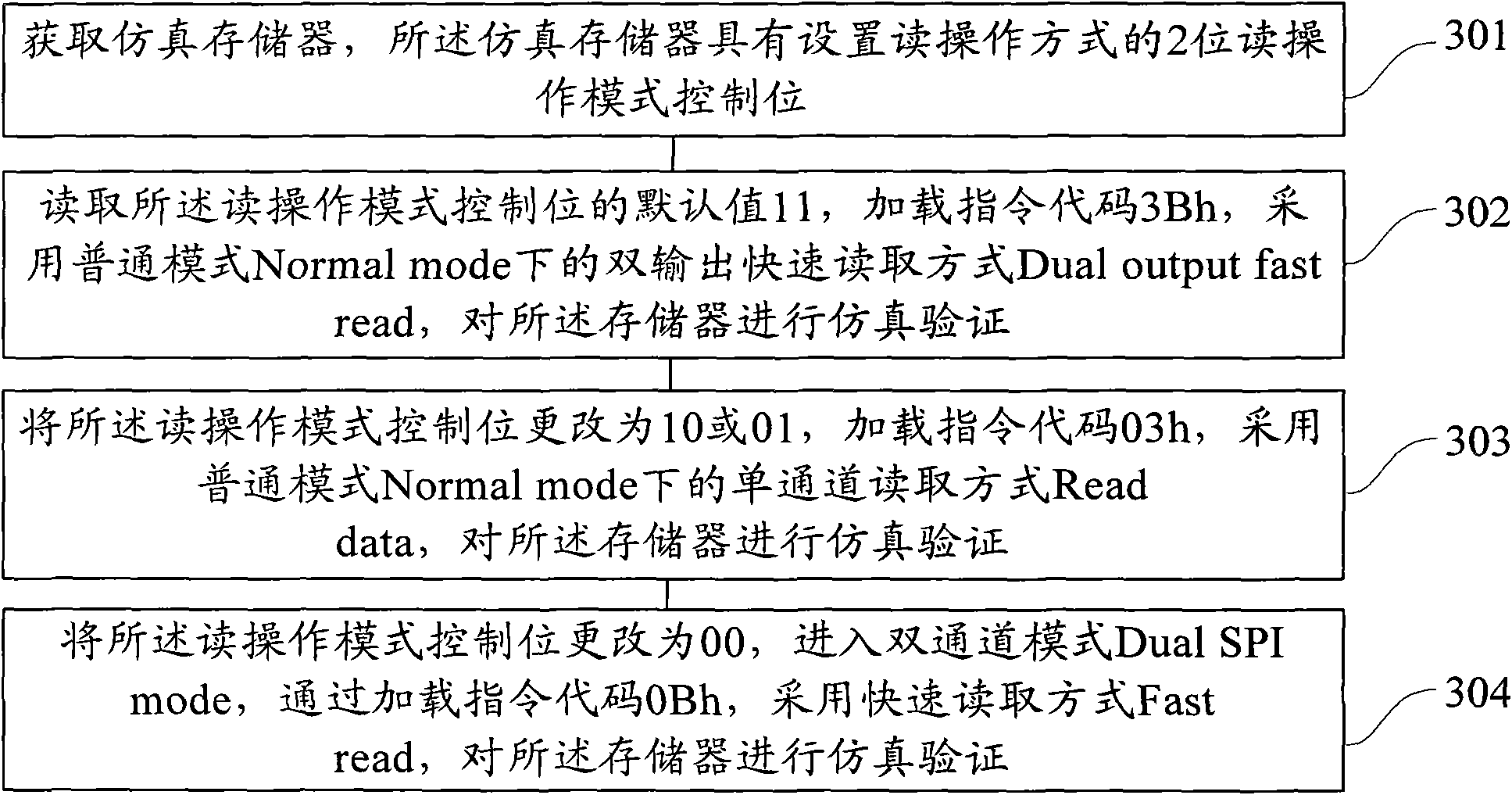

[0045] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0046]The following briefly introduces the three read operation modes of the memory.

[0047] The first type: Read data

[0048] In Normal mode, the corresponding read operation mode control bits are set to:

[0049] DSPI_LOCK=1, DREAD_LOCK=1;

[0050] Or, DSPI_LOCK=0, DREAD_LOCK=0.

[0051] In this read operation mode, DI_PAD is an input port, send an 8-bit command (03h), and after the 24-bit first address, the data will be output from DO_PAD (output port).

[0052] The second type: Fast read

[0053] In Normal mode, the corresponding read operation mode control bit is set to:

[0054] DSPI_LOCK=1, DREAD_LOCK=1,

[0055] Or, DSPI_LOCK=0, DREAD_LOCK=0.

[0056] In this read operation mode, DI_PAD is the input port, after se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More