Surging suppression circuit

A surge suppression circuit and resistor technology, applied in circuit devices, emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, etc. The effect of reducing power loss, suppressing injection, and real-time current limiting protection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

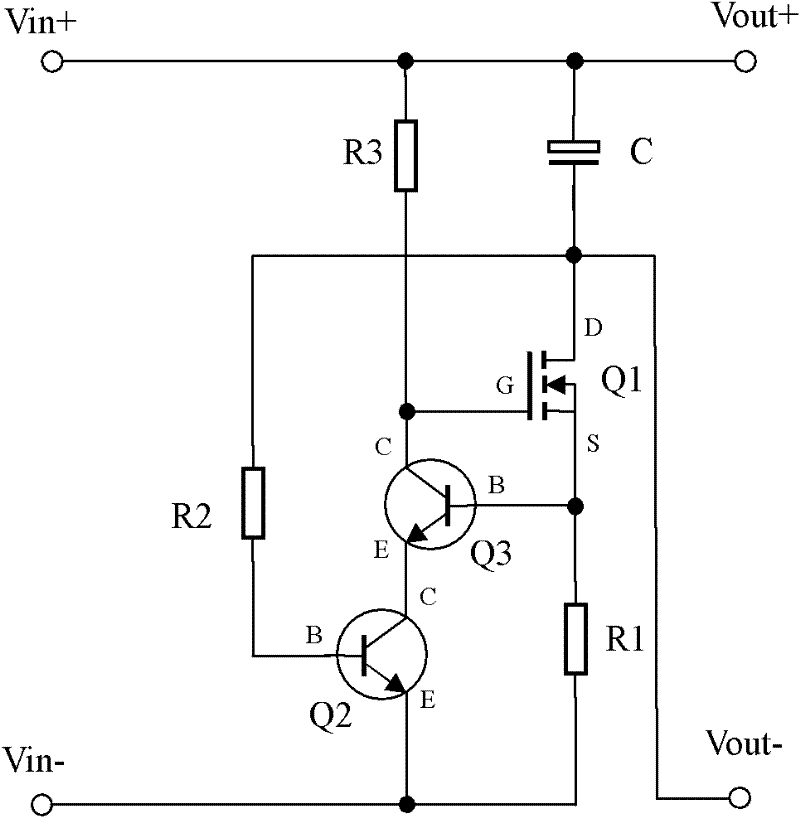

[0035] Such as figure 2 As shown, a surge suppression circuit includes a positive input terminal Vin+, a negative input terminal Vin-, a positive output terminal Vout+, a negative output terminal Vout-, a MOS transistor Q1, a second transistor Q2, a third transistor Q3, a capacitor C, The first resistor R1, the second resistor R2, and the third resistor R3, the positive input terminal Vin+ is connected to the positive output terminal Vout+, the positive input terminal Vin+ passes through the third resistor R3 and is connected to the gate of the MOS transistor Q1 and the third transistor Q3. Electrode connection, the positive input terminal Vin+ is connected to the drain of the field effect transistor Q1 through the capacitor C, the drain of the MOS transistor Q1 is also connected to the negative output terminal Vout-, the negative input terminal Vin- is connected to the source of the MOS transistor Q1 through the first resistor R1 The base of the third transistor Q3 is connecte...

Embodiment 2

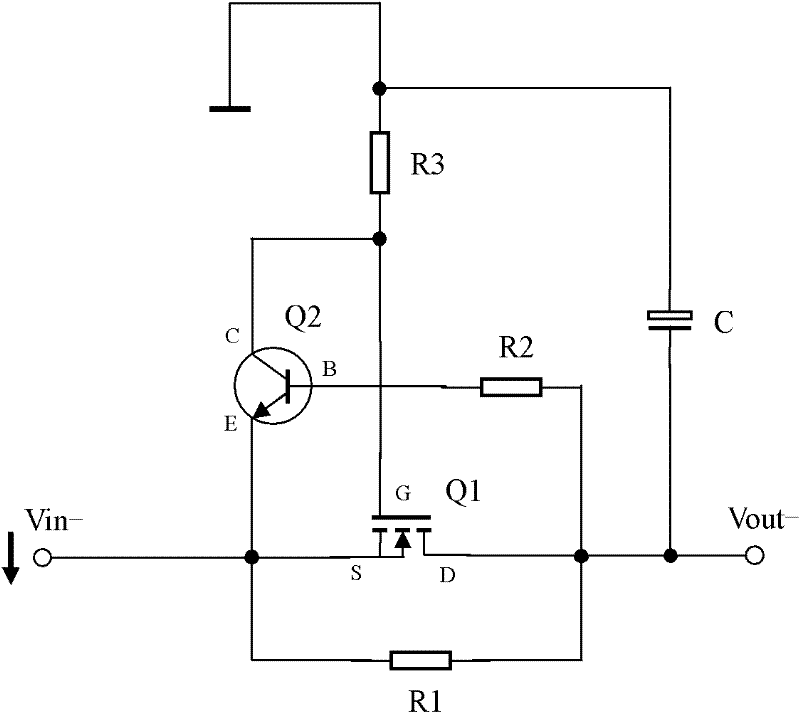

[0050] Such as image 3 As shown, the difference from the first embodiment is that the second transistor Q2 and the third transistor Q3 are PNP transistors, and the MOS transistor Q1 is a P-channel power MOS transistor. The power supply polarity should be reversed, and the other connection relations remain unchanged. If the capacitor uses a polarized capacitor such as an electrolytic capacitor, it can be connected according to the actual polarity when connecting.

[0051] Its working principle is the same as that described in the first embodiment, and will not be repeated here. The second embodiment is suitable for a circuit for controlling the input of a positive power supply, and a circuit where the input terminal and the output terminal need to share the ground.

[0052] In addition, the above two embodiments can be further improved. For example, connecting resistors in parallel between the base and emitter of the second transistor Q2 and the third transistor Q3 can adjust the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More